-

Maximize Design Productivity using Vivado ML with SystemVerilog

Although SystemVerilog is perhaps most widely used in the context of hardware verification, it also contains many features directly relevant to FPGA hardware designers. We explore the features of SystemVerilog that are useful for RTL synthesis using Vivado™ ML Editions from AMD, showing how the RTL SystemVerilog language constructs have been optimized for productivity and reliability.… Maximize Design Productivity using Vivado ML with SystemVerilog

-

QuantumATK V-2023.09 Release: Highlights of New and Enhanced Features

Join our FREE online event to learn about the new and enhanced features and performance improvements in the latest QuantumATK V-2023.09 product release. - Enhanced ease-of-use of training Machine-Learned FFs with new predefined Workflow Builder blocks and templates - New interactive Interfaces Builder for building multilayer structures - New Accelerated molecular dynamics method for crystallization… QuantumATK V-2023.09 Release: Highlights of New and Enhanced Features

-

Efficient Bluespec RISC-V Processor Verification for Highest Coverage Closure: A Comprehensive Case Study

The ability to mix and match multiple ISA extensions and add user-defined ISA extensions makes RISC-V verification more challenging than conventional processor verification. This Synopsys webinar demonstrates the verification of standard RISC-V ISA extensions. A subsequent webcast will demonstrate custom ISA verification. The multiple ISA verification problem is solved by RISCV-DV with configurability for ISA… Efficient Bluespec RISC-V Processor Verification for Highest Coverage Closure: A Comprehensive Case Study

-

UCIe-Based Chiplet Verification – from IP to SoC

Innovative die disaggregation technologies, enable a future where a catalog of chiplets will be available to mix and match based on the end application. The industry’s fastest emerging interconnect standard called Universal Chiplet Interconnect Express (UCIe) enables end users to combine chiplets with different functionality and technology nodes to develop highly sophisticated electronic chips. Hence,… UCIe-Based Chiplet Verification – from IP to SoC

-

SNUG Singapore 2023

ParkRoyal on Beach Road 7500 Beach Rd, Singapore, SingaporeSince 1991, the Synopsys Users Group (SNUG) has represented a global design community focused on innovating from Silicon to Software. Today, as the electronics industry’s largest user conference, SNUG brings together over 12,000 Synopsys tool and technology users across North America, Europe, Asia, and Japan. In addition to peer-reviewed technical presentations and insightful keynotes from… SNUG Singapore 2023

-

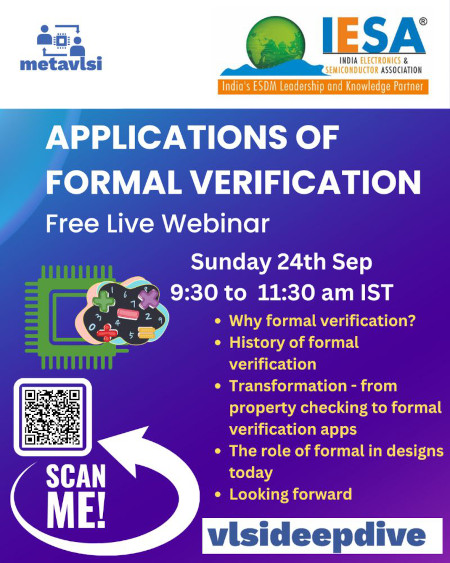

Applications of Formal Verification

It is an exciting time to explore a career in the VLSI semiconductor sector, and we're here to help you gain clarity on buzz and provide information on educational options towards a successful entry to this field with long-term career prospects. Design Verification is one of the essential and most promising career options. In the… Applications of Formal Verification

-

20th International Conference on IC Design and Technology (ICICDT)

University of Tokyo 7 Chome-3-1 Hongo, Tokyo, Japan2023 ICICDT is the twentieth edition (20th) in the series of the International Conference on IC Design and Technology, organized since 2004. 2023 ICICDT will be co-organized and held at the University of Tokyo, Tokyo, Japan from September 25-27, 2023. Design and technology co-optimization (DTCO) plays a critical role in the era of big data… 20th International Conference on IC Design and Technology (ICICDT)

-

Unleashing Innovation with UCIe

Exploring the Next Frontier in Chip Integration Webinar Agenda : Introduction to all UCIe layers Decrypting FLITs, PHY Trainings, Bring up flows FDI-RDI , main band and side band FLIT transfers etc. Implementation of Stacks-Arbiter, Retry mechanism & Retimer implementations Showcasing UCie FLIT transfer flow between multidies Enhancements done in UCIe 1.1 Who Should Attend:… Unleashing Innovation with UCIe

-

Synopsys VSO.ai Virtual Workshop

Virtual workshop with hands-on labs Achieving coverage closure continues to remain a challenge for customers and there is a growing need for a system to work autonomously to reach the target as quickly and cheaply as possible with the highest quality of results. The recently released Synopsys VSO.ai address this challenge in addition to inferring… Synopsys VSO.ai Virtual Workshop

-

TSMC 2023 North America OIP Ecosystem Forum

Santa Clara Convention Center 5001 Great America Parkway, Santa Clara, CA, United StatesLearn About: Emerging advanced node design challenges and corresponding design flows and methodologies for N2, N3/N3E/N3P/N3AE, N4/N4P, N5/N5A, N6/N6e/N6RF/N7, N12e, and N22 Latest updates on TSMC 3DFabric™ chip stacking and advanced packaging processes, InFO, CoWoS®, and SoIC, 3DFabric Alliance, and 3Dblox™ standard, plus innovative 3Dblox-based design enablement technologies and solutions, targeting HPC, AI/ML, and mobile… TSMC 2023 North America OIP Ecosystem Forum

-

Cadence Training: Cerebrus Intelligent Chip Explorer

Please join me, Cadence Training and Application Engineer Krishna Atreya, for this free technical Training Webinar. What Is the Webinar About? The Cadence Cerebrus Intelligent Chip Explorer is a revolutionary, machine learning-driven, automated approach to chip design flow optimization. Block engineers specify the design goals, and Cadence Cerebrus intelligently optimizes the Cadence digital full flow… Cadence Training: Cerebrus Intelligent Chip Explorer

-

Stratus HLS Automated Power Shutoff to Minimize Power and Retention Registers

Power Shutoff is a popular technique for saving power during functionally idle periods. Implementing Power Shutoff requires a detailed understanding of which resisters must be retained to enable bring-up from the power-off state. Identifying the minimal set of retention registers is challenging and grows more difficult with design complexity. This CadenceTECHTALK introduces a novel High-Level… Stratus HLS Automated Power Shutoff to Minimize Power and Retention Registers

12 events found.