-

-

Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration

Overview Title: Unveiling the Secrets to Proper Version Control, Seamless Data Integration, and Effective Collaboration Date: Wednesday, August 23, 2023 Time: 10:00 AM Pacific Time Duration: 30 minutes (+15 minutes live Q/A) Join us on Wednesday, August 23rd, to learn how to master semiconductor design success as we unveil the secrets to proper version control, seamless data integration, and… Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration

-

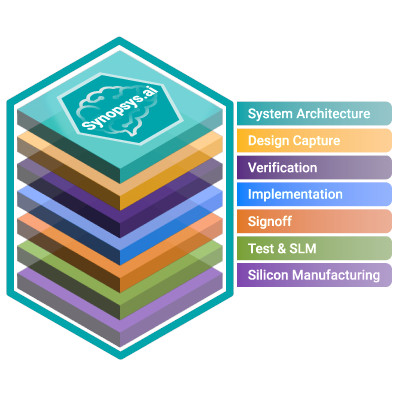

Optimize Test QoR & TTM with AI-Driven Technology

Continuously increasing semiconductor design sizes and complexity have resulted in increased test costs. Today’s competitive environment and critical market windows are pushing companies to adopt aggressive design schedules. The traditional method of manual iterations and fine-tuning test configurations to optimize test quality-of-results (QoR) is highly unpredictable and inefficient. Engineers can no longer rely on such… Optimize Test QoR & TTM with AI-Driven Technology

-

IP Lifecycle Management for Chiplet-Based SoCs

Chiplet-based SoC architectures have seen increased interest over the past three years, and recently were made a focus of the federal CHIPS and Science Act to reduce the cost of innovation for US-based semiconductor startups, DoD projects, and academic research. Chiplet-based architectures bring their own set of challenges however, especially in the context of IP… IP Lifecycle Management for Chiplet-Based SoCs

-

Virtuoso Studio and Signoff Technology Day

Cadence Design Systems, Building 5 2655 Seely Avenue, San Jose, CA, United StatesJoin us at CadenceCONNECT™: Virtuoso Studio and Signoff Technology Day focusing on our latest technology within the new Cadence® Virtuoso® Studio. Date: Thursday, August 24, 2023 Time: 8:30am – 5:00pm Location: Cadence Design Systems, San Jose, CA | Building 5 Learn how the best analog tools just got better to help you keep pace with… Virtuoso Studio and Signoff Technology Day

-

Hot Chips 2023

Stanford University 471 Lagunita Drive, Stanford, CA, United StatesHot Chips 2023 (advance program) will be held as a hybrid conference with in-person attendance at Stanford University from August 27 to 29, 2023. Conference Format Hot Chips 2023 will be a hybrid conference. You may register to attend virtual or in-person. The conference venue is the Dinkelspiel Auditorium on the Stanford University Conference. Sunday… Hot Chips 2023

-

GlobalFoundries Technology Summit 2023

San Jose Marriott 301 S Market Street, San Jose, CA, United StatesRegister now and join us at GlobalFoundries Technology Summit 2023! GF Technology Summit (GTS) 2023 is our worldwide, annual series of technology-focused events. GTS brings together leaders from the commercial, business and research worlds to understand the latest technology challenges and opportunities, and partner to create the most innovative applications and solutions. GTS 2023 Highlights This year's… GlobalFoundries Technology Summit 2023

-

High-Speed Channel Signal Integrity Optimization

Join our webinar as we share new optimization techniques to improve the efficiency and performance of your designs. The Optimality™ Explorer in the the Clarity™ 3D workbench allows users to navigate the design space with a panoramic view that can compensate for many years of engineering experience with an AI/ML-based optimization engine. During our webinar,… High-Speed Channel Signal Integrity Optimization

-

UCIe-Based Chiplet Verification – from IP to SoC

Innovative die disaggregation technologies, enable a future where a catalog of chiplets will be available to mix and match based on the end application. The industry’s fastest emerging interconnect standard called Universal Chiplet Interconnect Express (UCIe) enables end users to combine chiplets with different functionality and technology nodes to develop highly sophisticated electronic chips. Hence,… UCIe-Based Chiplet Verification – from IP to SoC

-

Four Important Signal Integrity Principles Demonstrated with Virtual Prototypes

Signal integrity encompasses all the problems that arise when interconnects are not electrically transparent. One difficulty in understanding signal integrity principles is that these effects can't be seen, felt, or heard. Visualizing the fields using 3D full wave simulations helps to build intuition immediately. While visualization is no substitute for understanding the electromagnetic principles at… Four Important Signal Integrity Principles Demonstrated with Virtual Prototypes

-

Accelerating Mainstream Adoption of Multi-Die Systems

Synopsys recently hosted a panel discussion with Ansys, Bosch, Intel, and Samsung to share their insights on the rapid adoption of multi-die systems. We invite you to the public broadcast of the panel where each company shares their view on the groundbreaking technology, what challenges lie ahead, and how companies can realize the promise of… Accelerating Mainstream Adoption of Multi-Die Systems

-

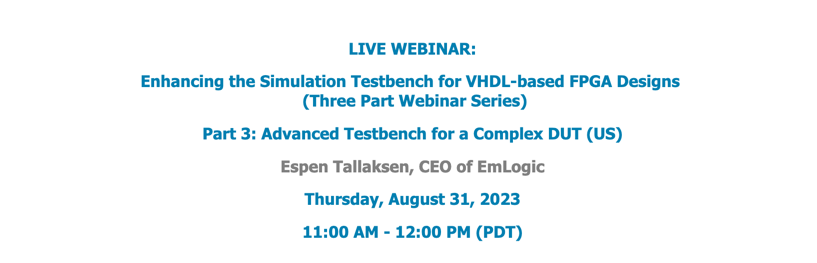

Advanced Testbench for a Complex DUT

Abstract: Functional simulation using an HDL testbench is the de facto method for proving functional correctness of FPGA designs. In this three-part webinar series, we will present a step-by-step approach on how to architect a testbench – progressing from basic to advanced techniques. We will first use a simple DUT then go to a more… Advanced Testbench for a Complex DUT

-

Advanced Testbench for a Complex DUT

Functional simulation using an HDL testbench is the de facto method for proving functional correctness of FPGA designs. In this three-part webinar series, we will present a step-by-step approach on how to architect a testbench – progressing from basic to advanced techniques. We will first use a simple DUT then go to a more complex… Advanced Testbench for a Complex DUT

12 events found.