-

-

Advanced Analog Design Using S-parameters

This webinar highlights the importance of S-parameters to IC design and how Semtech Corporation, a high-performance semiconductor, IoT systems and Cloud connectivity service provider, utilizes Siemens AFS XT simulation technology… Advanced Analog Design Using S-parameters

-

ERI 2.0 Summit

Hyatt Regency Seattle 805 Howell Street, Seattle, WA, United StatesWatch as leaders from our government agencies, the Defense Industrial Base, and prestigious universities bring unique and indispensable perspectives on our domestic semiconductor industry, national and economic security, and future… ERI 2.0 Summit

-

MIPI A-PHY & MASS – Revolutionizing Automotive Connectivity

1) Intro - MASS introduction 2) Usage - Full chip automotive systems from peripheral to processor and vice versa. E.g.Used in Radar, LiDAR, ADAS , etc. 3) APHY - PHY& Link layer… MIPI A-PHY & MASS – Revolutionizing Automotive Connectivity

-

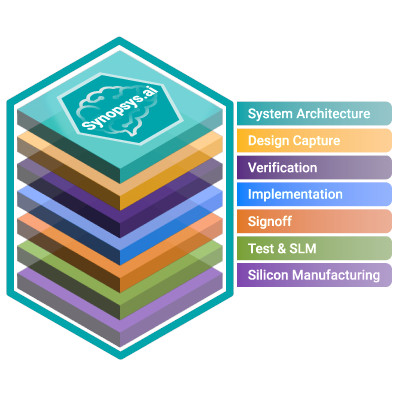

Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration

Overview Title: Unveiling the Secrets to Proper Version Control, Seamless Data Integration, and Effective Collaboration Date: Wednesday, August 23, 2023 Time: 10:00 AM Pacific Time Duration: 30 minutes (+15 minutes live Q/A) Join… Unveiling the Secrets to Proper Version Control, Seamless Data and Tool Integration, and Effective Collaboration

-

Optimize Test QoR & TTM with AI-Driven Technology

Continuously increasing semiconductor design sizes and complexity have resulted in increased test costs. Today’s competitive environment and critical market windows are pushing companies to adopt aggressive design schedules. The traditional… Optimize Test QoR & TTM with AI-Driven Technology

-

IP Lifecycle Management for Chiplet-Based SoCs

Chiplet-based SoC architectures have seen increased interest over the past three years, and recently were made a focus of the federal CHIPS and Science Act to reduce the cost of… IP Lifecycle Management for Chiplet-Based SoCs

-

Virtuoso Studio and Signoff Technology Day

Cadence Design Systems, Building 5 2655 Seely Avenue, San Jose, CA, United StatesJoin us at CadenceCONNECT™: Virtuoso Studio and Signoff Technology Day focusing on our latest technology within the new Cadence® Virtuoso® Studio. Date: Thursday, August 24, 2023 Time: 8:30am – 5:00pm… Virtuoso Studio and Signoff Technology Day

-

Hot Chips 2023

Stanford University 471 Lagunita Drive, Stanford, CA, United StatesHot Chips 2023 (advance program) will be held as a hybrid conference with in-person attendance at Stanford University from August 27 to 29, 2023. Conference Format Hot Chips 2023 will… Hot Chips 2023

-

GlobalFoundries Technology Summit 2023

San Jose Marriott 301 S Market Street, San Jose, CA, United StatesRegister now and join us at GlobalFoundries Technology Summit 2023! GF Technology Summit (GTS) 2023 is our worldwide, annual series of technology-focused events. GTS brings together leaders from the commercial, business and… GlobalFoundries Technology Summit 2023

-

High-Speed Channel Signal Integrity Optimization

Join our webinar as we share new optimization techniques to improve the efficiency and performance of your designs. The Optimality™ Explorer in the the Clarity™ 3D workbench allows users to… High-Speed Channel Signal Integrity Optimization

-

UCIe-Based Chiplet Verification – from IP to SoC

Innovative die disaggregation technologies, enable a future where a catalog of chiplets will be available to mix and match based on the end application. The industry’s fastest emerging interconnect standard… UCIe-Based Chiplet Verification – from IP to SoC

-

Four Important Signal Integrity Principles Demonstrated with Virtual Prototypes

Signal integrity encompasses all the problems that arise when interconnects are not electrically transparent. One difficulty in understanding signal integrity principles is that these effects can't be seen, felt, or… Four Important Signal Integrity Principles Demonstrated with Virtual Prototypes

12 events found.