Webinar

-

-

Reimagining Synopsys SLM PVT Monitoring IP for Advanced Node GAA Process

Synopsys' SLM PVT Monitor (process detector, voltage monitor, temperature sensor) IP can collect voltage, temperature, and process parameters from different blocks within the IC in real time. These data can be analyzed and used to take meaningful action to optimize the performance of the chip at any stage of silicon lifecycle. This webinar focuses on… Reimagining Synopsys SLM PVT Monitoring IP for Advanced Node GAA Process

-

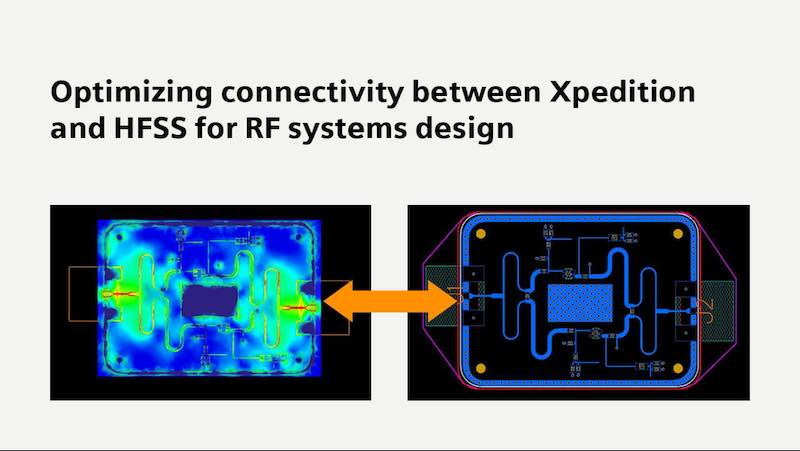

Optimizing connectivity between Xpedition and HFSS for RF systems design

In today's fast-paced technological landscape, seamless integration between design and simulation tools is crucial for accelerating product development cycles and ensuring optimal performance of electronics, especially RF systems. Siemens Xpedition and Ansys HFSS stand as pillars in their respective domains, offering powerful capabilities for electronic design and electromagnetic simulation. In this live conversation, Sara Louie… Optimizing connectivity between Xpedition and HFSS for RF systems design

-

Addressing Real-Time Workloads in Automotive Applications with Efficient ARC-V Processors

Many automotive applications require processing workloads with minimum latency and precise timing budgets. This is especially true for safety-critical applications like adaptive cruise control and anti-lock braking, where human life may be jeopardized. These systems require processing elements that can respond to events within specific (predictable) time constraints. System reliability and availability depend on the… Addressing Real-Time Workloads in Automotive Applications with Efficient ARC-V Processors

-

-

Silicon.da: The First Integrated SLM Analytics Solution from Design Through Manufacturing

Today’s advanced node chip designs are faced with many new complexities which require more verification, more validation and more analysis. The resulting data from these added steps has also grown exponentially and engineers need a way to efficiently analyze this information. The result is a new paradigm shift which has led to data overload requiring… Silicon.da: The First Integrated SLM Analytics Solution from Design Through Manufacturing

-

Addressing Thermal Stress and Warpage Challenges in 3D-IC Designs

Thermal stress analysis plays a crucial role in the design and performance optimization of packaging materials and boards, especially in industries where temperature variations are significant. This webinar presents a comprehensive overview of recent developments in the newly-introduced Cadence Celsius Studio AI-enabled multiphysics thermal platform to solve today’s thermal stress and warpage analysis in 3D-ICs.… Addressing Thermal Stress and Warpage Challenges in 3D-IC Designs

-

Design, Manage, and Share Data with OrCAD X Cloud Workspaces

The OrCAD X platform allows you to manage and collaborate throughout the PCB design process. The cloud workspaces are available out-of-the-box without any additional setup of internal/external server dependencies. If you are a Librarian, Electrical Engineer, or a member of the PCB design team, Join us for this webinar to learn more about library and… Design, Manage, and Share Data with OrCAD X Cloud Workspaces

-

Developing Silicon Carbide DMOSFETS: A Digital Twin Reference Flow

This webinar presents a comprehensive methodology for the design and optimization of a 1200V Silicon Carbide (SiC) Double-Diffused Metal-Oxide-Semiconductor Field-Effect Transistor (DMOS FET) utilizing Silvaco's TCAD platform. Adhering to industry best practices, the construction of an accurate digital twin is also presented, ensuring conformity to real-world performance characteristics. Moreover, we outline strategies to streamline simulation… Developing Silicon Carbide DMOSFETS: A Digital Twin Reference Flow

-

Developing Silicon Carbide DMOSFETS: A Digital Twin Design Reference Flow

This webinar presents a comprehensive methodology for the design and optimization of a 1200V Silicon Carbide (SiC) Double-Diffused Metal-Oxide-Semiconductor Field-Effect Transistor (DMOS FET) utilizing Silvaco's TCAD platform. Adhering to industry best practices, the construction of an accurate digital twin is also presented, ensuring conformity to real-world performance characteristics. Moreover, we outline strategies to streamline simulation… Developing Silicon Carbide DMOSFETS: A Digital Twin Design Reference Flow

-

-

How to Reduce Thousands of False Errors in 15 Minutes

Analyzing electrical errors across an IP or a SoC at top level, can be a painful and long process, often requiring extensive setup time and hundred of hours to distinguish real issues from false positives. To address this challenge, Aniah developed OneCheck, a formal analysis tool capable of detecting 100% of electrical errors at the… How to Reduce Thousands of False Errors in 15 Minutes

-

Ensuring my Design Verification is ISO26262 Compliant

Cadence, Bengaluru Sarjapur Outer Ring Road, Bengaluru, IndiaWith the widespread of the modern automobiles, run and regulated by automotive ECUs, the need for advanced safety features has also become inevitable. And this is why today modern vehicles are required to adhere to the safety standards listed within the Automotive Safety Integrity Level (ASIL).In this DVClub meeting our speakers will share best practices… Ensuring my Design Verification is ISO26262 Compliant

-

Maximize Productivity with Deep Insights into PPA Trajectories

The digital chip design flow carries with it an enormous wealth of untapped information regarding the health and status of your SoC design. The ability to efficiently mine this data provides chip designers with comprehensive visibility and actionable insights to uncover PPA opportunities. This webinar will introduce you to Synopsys Design.da, the industry’s first comprehensive data-visibility… Maximize Productivity with Deep Insights into PPA Trajectories

-

Efficient Way to UVM Constraint Randomization Debug

Become skilled at the art of UVM randomization debugging! Date: Wednesday, July 17, 2024 Time: 10:00am PDT | 1:00pm EDT This webinar equips you with effective strategies to tackle randomization-related errors within your UVM verification environment. We'll explore the power of Cadence's Verisium Debug, a tool designed to simplify the debugging process. What You Will Learn Practical… Efficient Way to UVM Constraint Randomization Debug