2.5D Packaging

Events

-

-

Protocol and Memory Interface Verification in the Shrinking World of 3DIC

Emerging 2.5D and 3DIC packaging technologies enable more design complexity, and bring some new verification challenges. We look at how to scale your verification capability to match and how to plan ahead for verification of die-to-die interconnect protocols such as UCIe and memory verification with HBM. Packaging technologies for 2.5D and 3DIC are becoming more…

-

-

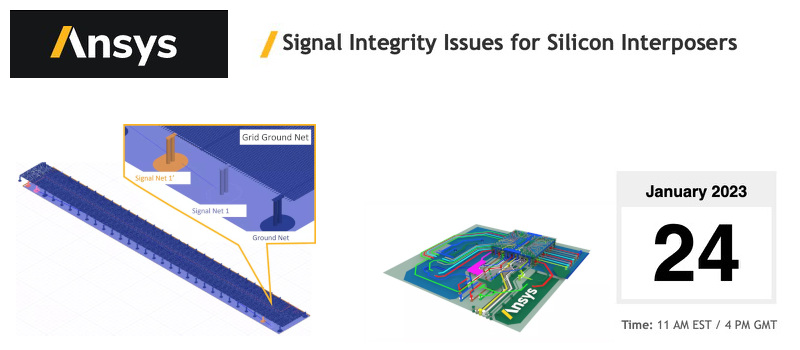

Signal Integrity Issues for Silicon Interposers

The development of applications like high-performance computing, Artificial Intelligence (AI) processors, and Central Processing Unit (CPU) and Graphical Processing Unit (GPU) chips involves advanced packaging technologies that radically alter traditional design methodologies and flows. Designers of high-speed components are called to co-simulate die, interposers, and package to sign off for their products' signal integrity (SI)…