FPGA

Events

-

-

UVM for FPGAs (Part 2): Solving FPGA Verification Challenges with UVM

Abstract: Today’s FPGAs have become larger in logic density and can handle complex designs with multi-million system logic cells. The traditional verification techniques of simple simulations combined with a detailed validation in the lab simply do not scale up any longer. Even to map a large logic design to a modern-day FPGA takes many hours.…

-

-

UVM for FPGAs (Part 4): IEEE 1800.2 UVM Updates

Abstract: Started with an early adaptor release as Accellera 1.0a, UVM has evolved into few significant versions including UVM 1.1 and UVM 1.2. As with many popular useful standards, UVM has attained the coveted IEEE standardization in 2017. Interestingly, UVM is the first verification methodology to be standardized, and the current version is IEEE 1800.2-2020.…

-

CHIPS Alliance Workshop

CHIPS Alliance, the open source RTL hardware and software development tool organization, is gathering to share milestones, progress, updates and more.

-

The most error prone FPGA corner cases

Presenter: Espen Tallaksen, CEO of EmLogic Thursday, October 14, 2021 Abstract: Cycle related corner cases are probably the worst and main reason for undetected bugs on many FPGAs. To explain this in a simple way, - a cycle related corner case is for instance if you have an event counter where the number of counted…

-

VSDOpen 2021 Online Conference

What is VSDOpen 2021 Agenda? Key strategy - Provide High Tech Experience of developing analog designs using Open-Source Tools, PDKs and Cloud Platform 3 days of Conference Tutorials Key Focus – Analog Products, Open-source FPGA and Semiconductor IP's Keynote Speaker – Industry leaders focused on Developing IoT, 5G and AI products, Professor from open-source Research…

-

-

FPGA Conference and Hackathon

We are changing the world through this. So you can! Join the FPGA Hackathon we organize in Kraków to learn more about the technology gaining more and more popularity! Sharing this passion is the reason why we decided to create this Conference and Hackathon. FPGA technology is one of the foundations for the revolutionary projects…

-

-

LIVE WEBINAR: How to Simplify the Verification of Bus Interfaces (US)

Abstract: Today’s FPGAs and SoC FPGAs use various types of bus interconnect - such as AXI, APB, AHB, Avalon or Wishbone - for both internal (IP-level) and external communication. A recently added feature to Aldec’s ALINT-PRO allows designers to extract, review and verify the correctness of bus interface connections. In addition, ALINT-PRO is capable of…

-

How to Overcome the Pain Points of AI/ML Hardware Design

Join Achronix for a live Webinar December 16th: 10-11 AM Pacific and Recorded On-Demand After the Event AI/ML hardware faces three common pain points: memory bandwidth, computational throughput and on-chip data movement. Next-generation FPGA technology includes a 2D network on chip, GDDR6 memory interfaces and high performance machine learning processors, which present new capabilities to…

-

-

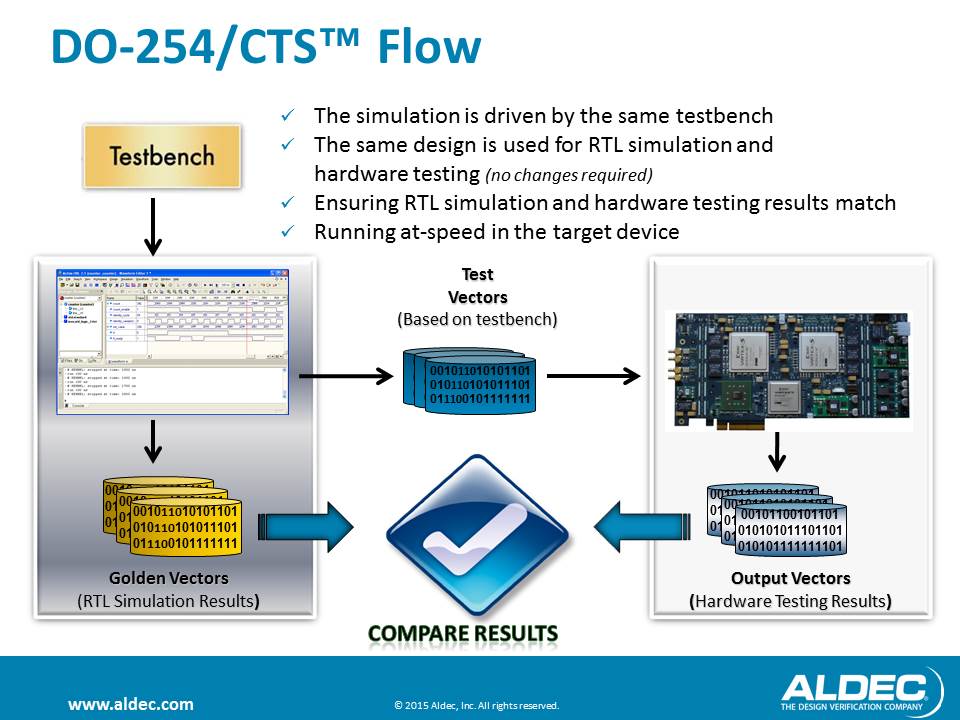

Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance (US)

PCIe-based FPGA designs are becoming popular within avionics systems. However, the verification of such designs for DO-254 compliance with design assurance level (DAL) A or B is problematic. FPGA designs that use asynchronous clocks with multiple high-speed serial interfaces such as PCIe produce non-deterministic results during physical tests. Simulation results are optimized because they are…

-

Open-Source FPGA: Towards Fully Automated FPGA Tapeout Flows

In this webinar, we will present the open-source FPGA tools which automate the tapeout flow for custom FPGA fabrics. We will cover the key steps involved in the process when using the tools, including netlist generation, design verification and performance prediction. We will also introduce the latest features in open-source FPGA and explain how they…

-

FPGA 22

The ACM/SIGDA International Symposium on Field-Programmable Gate Arrays is a premier conference for presentation of advances in FPGA technology. Accepted papers will be published in the conference proceedings and available in the ACM Digital Library. Virtual Conference February 27 – March 1, 2022 Registration now open at: www.isfpga.org/registration Statement from the General Chair: We have made…

-

-

Using SVA for Requirements-Based Verification of Safety-Critical FPGA Designs

Requirements-based verification (RBV) is a popular verification process for FPGA designs used in safety-critical systems. The effectiveness of RBV is limited by the quality and precision of the requirements. Verification techniques such as constrained random verification with assertion-based verification (ABV) can be used to help identify ambiguous or incomplete requirements early in the design and…