- This event has passed.

Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance (US)

February 10, 2022 @ 11:00 am - 12:00 pm PST

PCIe-based FPGA designs are becoming popular within avionics systems. However, the verification of such designs for DO-254 compliance with design assurance level (DAL) A or B is problematic. FPGA designs that use asynchronous clocks with multiple high-speed serial interfaces such as PCIe produce non-deterministic results during physical tests. Simulation results are optimized because they are based on simplified models, while the test results in physical hardware depend on the phases of clock oscillators. Bit-level verification struggles with this, especially when comparing physical test results against simulation results for traceability, and many false errors are likely to be observed.

In this webinar we will introduce transaction-level methodology (TLM), and how it can be used for verifying PCIe-based FPGA designs for DO-254 compliance. Transactions are easier to manage and correlate with the simulation results, therefore traceability is much easier to establish. Also, the untimed testbenches used with TLM are not sensitive to clock frequency and phase changes, which is ideal for verifying PCIe-based FPGA designs with non-deterministic behavior.

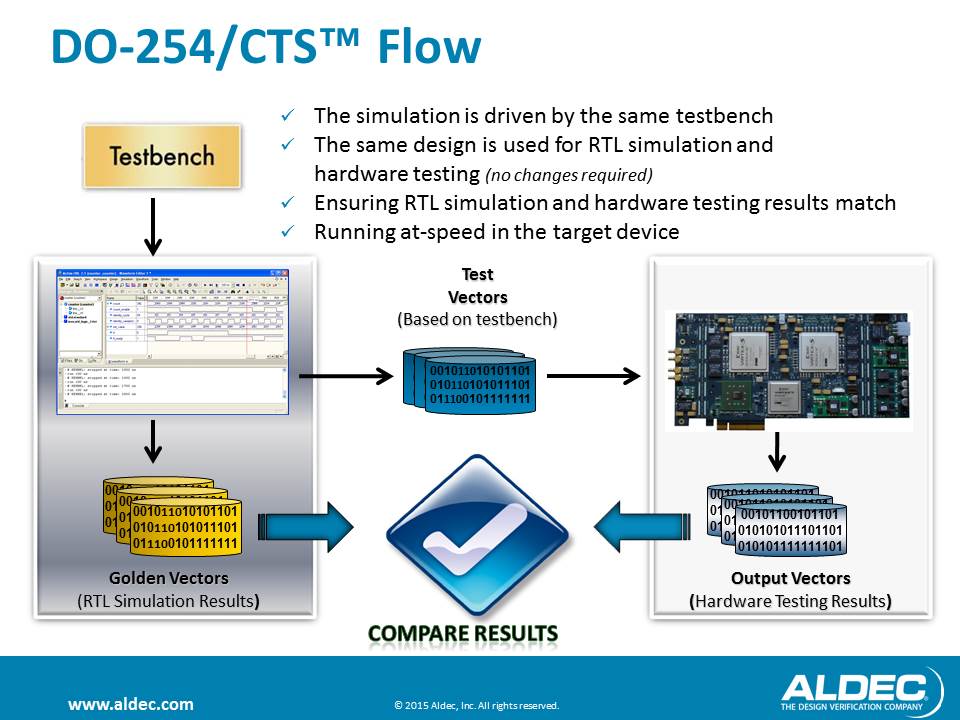

We will also show a complete flow using TLM from simulation all the way to target FPGA physical testing with our popular CTS platform.