SI/PI

Events

-

-

Conquer SI/PI Challenges and Reduce Time to Signoff for PCIe 6.0

The Peripheral Component Interconnect Express (PCIe®) high-speed interface has become the standard for computer expansion cards due to its high bandwidth combined with manageable component costs. However, the latest PCIe 6.0 release raises new challenges for design engineers, as the popular interface standard moves to pulse-amplitude modulation-4 (PAM-4) signaling for the first time. This webinar…

-

-

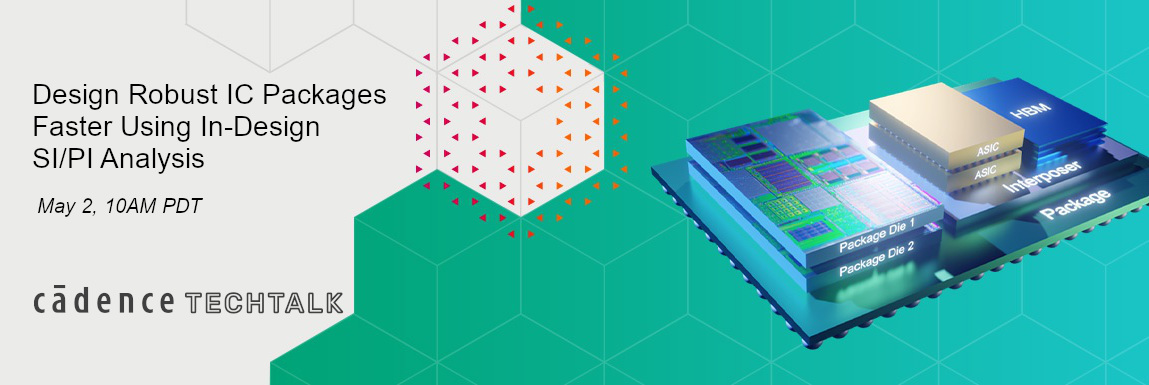

Design Robust IC Packages Faster Using In-Design SI/PI Analysis

IC package design teams and characterization teams have had a “throw-it-over-the-wall” relationship for decades, which often delays design releases by months. However, as signal integrity (SI) and power integrity (PI) challenges evolve with multi-die heterogeneous integration, the need to perform SI/PI analysis as part of the design flow has become a requirement to meet compressed…

-

-

Meet Advanced IC Package Design Schedule Challenges with In-Design Analysis

The heterogeneous integration of chips/chiplets has added significant complexity to the IC package design process, further compressing schedules for many design teams. Design teams must work more efficiently to meet quality and performance goals while maintaining schedule milestones. One way to improve efficiency is to shift signal and power integrity (SI/PI) analysis to earlier in…

-

-

Seamless SI/PI Signoff of Allegro PCB Designs Driven by In-Design Analysis

Signal and power integrity (SI/PI) are top priorities for engineers designing today’s high-speed, high-density PCBs. Easy-to-use in-design analysis directly integrated into the Allegro PCB design environment uncovers SI/PI issues early in the design process, leading to faster signoff of designs. With analysis shifting left in the design cycle, design teams can achieve efficient signoff of…

-

-

AI-Driven Constraint Generation for PCB and IC Package Design

Join our webinar to discover how AI-driven optimization and automation in constraint generation can boost productivity and shorten design cycles for PCB and IC package design. Learn how integrating Allegro X and Sigrity X can streamline your workflow. Key Takeaways: Learn how the Sigrity Topology Workbench, a robust system-level SI/PI environment for what-if and pre-route…

-

-

Signal and Power Integrity Challenges in Advanced Packaging Technologies for Disaggregated Integration

Abstract The integrated circuit industry faces new challenges as chip complexity and area have been increasing to prohibitive ranges. Some segments have been adopting then a relatively new paradigm for heterogeneous integration based on chiplets at the first package level in combination with advanced 2.5 and 3D packaging technologies. The chiplet approach has the advantage…