Verisium

Events

-

-

Verisium Debug for UPF Low Power Design

Verisium Debug offers comprehensive debugging capabilities. From RTL, UVM testbench to UPF low-power designs, users can use the Cadence unified debugging platform for debugging. In this webinar, users will learn about the available features in Verisium Debug for UPF power-aware designs and using the unique capabilities to visualize and debug UPF low-power designs. What you…

-

-

Verisium Debug for UVM Testbench

Verisium Debug offers comprehensive debugging capabilities. From RTL and UVM testbench to UPF low-power designs, Cadence’s unified debugging platform helps users debug. In this webinar, users will learn about the available features in Verisium Debug for UVM testbench and use these unique capabilities to visualize and debug the UVM testbench. What you will learn Understand…

-

-

Verisium SimAI: Coverage Gaps Meet Their Match

Every project has some areas that seem impossible to cover. Various factors can cause these nearly impossible-to-hit coverage gaps, including technical complexity, lack of resources, and shifting requirements. In constrained random environments, simply running more random seeds may not always address these coverage gaps effectively. Overcoming these gaps requires creativity, persistence, and technical expertise. A…

-

-

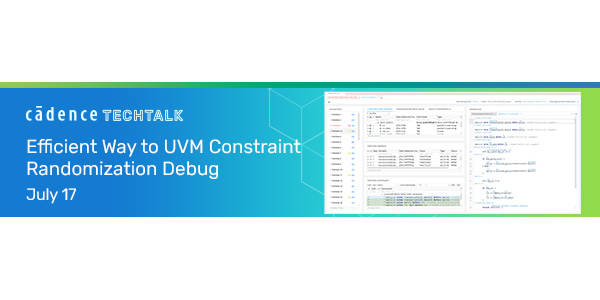

Efficient Way to UVM Constraint Randomization Debug

Become skilled at the art of UVM randomization debugging! Date: Wednesday, July 17, 2024 Time: 10:00am PDT | 1:00pm EDT This webinar equips you with effective strategies to tackle randomization-related errors within your UVM verification environment. We'll explore the power of Cadence's Verisium Debug, a tool designed to simplify the debugging process. What You Will Learn Practical…

-

-

Leveraging Verisium Debug to Debug Digital-Mixed Signal Designs

Many of today’s designs that are primarily digital also contain analog components. We refer to such designs as “Digital-Mixed-Signal” or DMS designs. In this webinar, we will demonstrate using the Verisium Debug App to debug such DMS designs. What You Will Learn How Verisium Debug supports debugging Xcelium (Real Number Modeling) RNM and mixed Xcelium…

-

-

Fast Track RTL Debug with the Verisium Debug Python App Store

Working with debugging scripts locally and manually can be challenging, as can reusing and organizing them. What if there was a way to create your own app with the required functionality and to register it with the tool? The answer lies in the Verisium Debug Python App Store. Instantly add additional features and capabilities to…