![]()

Dermott Lynch of Silicon Frontline spoke with me by phone on Monday to give an update about how their tools extract 3D accurate RC netlists. We first met at Viewlogic in the 90’s when Dermott was at Quad Designs and Viewlogic acquired the Motive static timing tool.

The first thing that impressed me about Silicon Frontline was the ex-Nassda founders, well-known for how they created the first hierarchical FastSPICE circuit simulator. I’ll never forget hearing about HSIM in 2000 at a memory account where their simulator could read an entire RAM netlist, while my FastSPICE tool at Mentor could only read a portion of the same netlist before running out of memory.

So, why create yet another extraction tool? Don’t we already have plenty of EDA companies offering extraction?

Great questions and what I learned was that extraction accuracy can mean the difference between simulating the circuit correctly or producing poor results that lead to silicon failures. Older tools created 10 years ago have been using pattern-matching to speed up extraction however it was at the expense of accuracy. On the other hand we could use 3D field solvers for highest accuracy but only on cells, not blocks or full chip.

This VC-backed company set it’s sights on providing a high-performance, high-capacity extraction tool for accuracy critical mixed-signal designs.

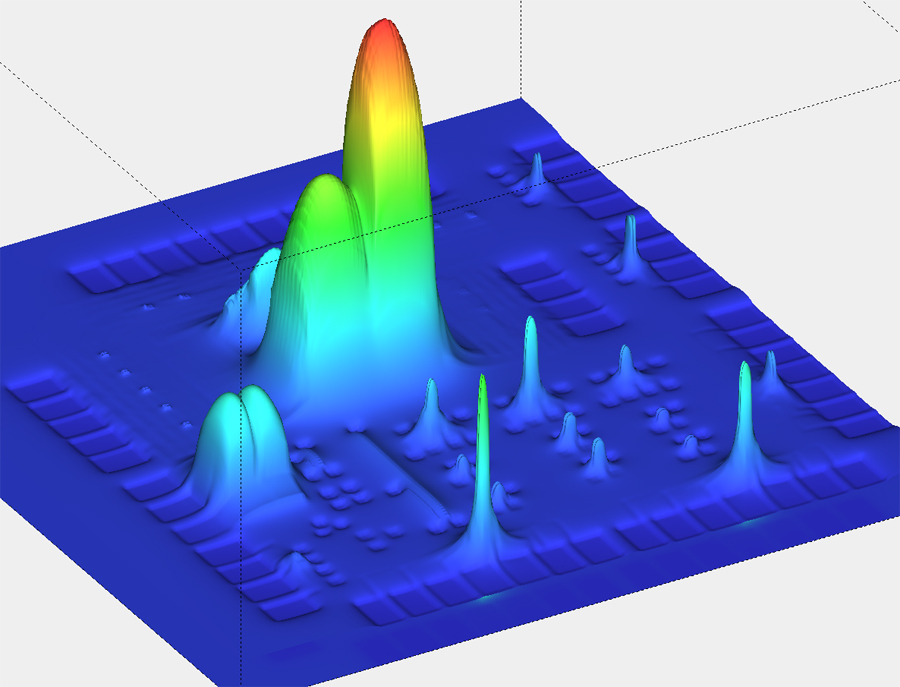

The secret sauce at Silicon Frontline is an extraction tool that approaches 3D field solver accuracy while being just a bit slower than traditional extraction tools.

Output from the extractor is an accurate RC netlist ready for circuit simulation in SPICE format or DSPF, IR drop analysis, or EM analysis. Look for inductors (L) to be added in a future release.

The RC values will approach what you see with tools like Raphael or QuickCAP. 3D field solvers also produce s-parameters which are frequency dependent, however the Silicon Frontline tools produce just RCs.

Their tools are multi-threaded and you can use 4 to 8 cores. Distributed processing will come a bit later.

The kind of designs that benefit most from this accurate netlist are: image sensors, power devices, ADCs (12-14 bits and more, using SPICE simulators with coupling), advanced processes (65nm and below).

F3D is the extractor tool name for mixed-signal designs. One customer SOC design in 65nm required just 10 hours to extract.

R3D is a special tool just for power device extraction. I even saw a DC analysis done with color graphs of current density (run Transient in your SPICE simulator). A customer design that took months for extraction and analysis now took only hours with this new tool. That’s productivity.

TSMC has approved these tools at the 65nm and 40nm nodes.

Patents have been filed, not granted, still pending.

Sales are direct in silicon valley, with distributors in Asia, Japan and Europe.

This start-up has 15 people now and looks to be in growth mode.

It will be interesting to see if Cadence, Mentor, Synopsys and Magma can respond to the new extraction tools at Silicon Frontline.

[…] Frontline saw this opportunity and announced products earlier this year to address 3D extraction (F3D) and 3D resistance for power devices (R3D). I spoke today with […]