-

How Deep Data Analytics Accelerates SoC Time-To-Market by 6 Months

This webinar will cover how using deep data analytics: Accelerates time-to-market by 20-25% (equivalent to six months in this example), ensuring the product is first to market and able to capitalize on this advantage. Reduces design and development costs by nearly $25M, amounting to a 9% cost savings. Leads to a higher quality product by improving performance by… How Deep Data Analytics Accelerates SoC Time-To-Market by 6 Months

-

CadenceTECHTALK: System-Level Thermal Signoff from Chips Through to Racks

Today’s modern electronic designs require ever more functionality and performance to meet consumer demand. These challenges become more critical and complex when resistive losses in PCB and package structures are significant since resistive losses are temperature dependent. In this webinar, we will look at an electrothermal co-simulation solution for the full hierarchy of electronic systems… CadenceTECHTALK: System-Level Thermal Signoff from Chips Through to Racks

-

The Path to 1.6TbE with 224G Ethernet PHY IP

The need for faster and more efficient Ethernet solutions has never been greater, as the demands of high-performance computing and the rise of big data continue to grow. Join us as we explore the main challenges faced in scaling Ethernet to 1.6T and how the high-performance computing is changing the Ethernet landscape. In this webinar,… The Path to 1.6TbE with 224G Ethernet PHY IP

-

The Power of VHDL’s VHPI

The programming interfaces of logic simulators are largely the domain of specialists writing proprietary tools and extensions and are only vaguely in the consciousness of many design and verification engineers, if aware at all. Yet the simplest use of such interfaces opens up a whole world of possibilities in extending what is achievable in verifying… The Power of VHDL’s VHPI

-

IEEE International Symposium on Hardware Oriented Security and Trust (HOST)

The DoubleTree by Hilton 2050 Gateway Place, San Jose, CA, United StatesIEEE International Symposium on Hardware Oriented Security and Trust (HOST) is the premier symposium that facilitates the rapid growth of hardware-based security research and development. Since 2008, HOST has served as the globally recognized event for researchers and practitioners to advance knowledge and technologies related to hardware security and assurance. Rapid proliferation of computing and communication… IEEE International Symposium on Hardware Oriented Security and Trust (HOST)

-

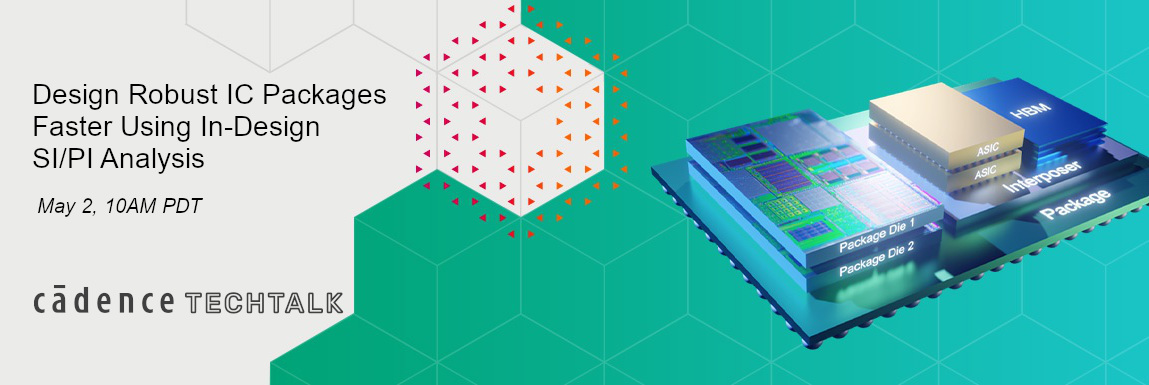

Design Robust IC Packages Faster Using In-Design SI/PI Analysis

IC package design teams and characterization teams have had a “throw-it-over-the-wall” relationship for decades, which often delays design releases by months. However, as signal integrity (SI) and power integrity (PI) challenges evolve with multi-die heterogeneous integration, the need to perform SI/PI analysis as part of the design flow has become a requirement to meet compressed… Design Robust IC Packages Faster Using In-Design SI/PI Analysis

-

SemIsrael Tech Webinar

Shine Chung Chairman Attopsemi Technology Revolutionary Metal I-fuse® OTP in FinFET Tech Umesh Sisodia CEO CircuitSutra Transforming Semiconductor Design Using SystemC Based Shift-left ESL Methodologies Roger Espasa CEO & FounderSemidynamics RISC-V, Out-of-Order IP Core, Vector Unit Siddharth Ravikumar Technical Product Manager, Solido IP ValidationSiemens EDA IP, QA, Validation, analog, digital, mixed-signal Michael Seaholm Product Manager… SemIsrael Tech Webinar

-

TSMC – Austin Technology Workshop

Omni Barton Creek Resort & Spa 8312 Barton Club Drive, Austin, TX, United StatesJoin us and learn about: TSMC's smartphone, HPC, IoT, and automotive platform solutions TSMC's advanced technology progress on 5nm, 4nm, 3nm, 2nm processes and beyond TSMC's specialty technology breakthroughs on ultra-low power, RF, embedded memory, power management, sensor technologies, and more TSMC 3DFabric™ advanced packaging technology advancement on InFO, CoWoS®, and SoIC TSMC's manufacturing excellence,… TSMC – Austin Technology Workshop

-

Basic Testbench for a Simple DUT

Presenter: Espen Tallaksen, CEO of EmLogic Abstract Part 1: Functional simulation using an HDL testbench is the de facto method for proving functional correctness of FPGA designs. In this three-part webinar series we will present a step-by-step approach on how to architect a testbench - progressing from basic to advanced techniques. We will first use… Basic Testbench for a Simple DUT

-

May 2023 Austin RISC-V Meetup

The Austin RISC-V Group is back, and we're planning a regular schedule of the second Tuesday of every month. This will be an on-line event. We'll be the RISC-V Bivy virtual meeting system, and this is the same as the event on the RISC-V Community site. The use of a microphone and/or camera are not… May 2023 Austin RISC-V Meetup

-

ChipEx 2023

Hilton Hotel Tel-aviv HaYarkon St 205, Tel aviv, IsraelThe major annual event of the Israeli semiconductor industry ChipEx2023, the largest annual event of the Israeli semiconductor industry, will be held on May 9, 2023 in Tel Aviv, Israel. ChipEx2023 showcases companies including manufacturers, developers and suppliers of advanced hardware technologies & services. It also includes a technical seminar where the world's leading experts address the industry's most relevant… ChipEx 2023

-

The 32nd Microelectronics Design and Test Symposium (MDTS 2023)

Crowne Plaza - Desmond Hotel 660 Albany Shaker Rd, Albany, NY, United StatesTheme Artificial Intelligence, Machine Learning, and Deep Learning: Tactical and Strategic Impacts to Microelectronics Design and Test About MDTS 2023 The IEEE Microelectronics Design & Test Symposium (MDTS) provides a forum for academic and industry researchers and engineers to discuss the latest advances in microelectronics, share their visions in modern microelectronic technologies, and foster academic-industry… The 32nd Microelectronics Design and Test Symposium (MDTS 2023)

12 events found.