-

-

Pre-empt Late-stage Low Power Issues using Predictive Analysis

Low power is an increasingly critical requirement for all modern SoCs. Moreover, it is becoming more and more difficult with complex architectures being used in modern designs. This has made it necessary for designers to invest heavily in this verification effort throughout the design development cycle starting from architecture definition, RTL development, to final netlist tape-out. Conventionally, static low power flow constitutes defining and cleaning… Pre-empt Late-stage Low Power Issues using Predictive Analysis

-

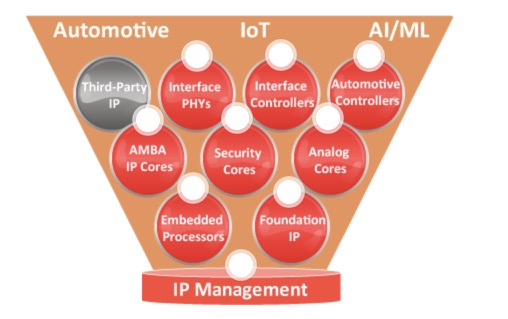

Designing with Silvaco’s Octal SPI Memory Controller with Advanced Memory Support for IoT Systems

Abstract One commonality across semiconductor market segments is the need for memory. However, memory characteristics and interfaces vary greatly depending on the market segment and application. This webinar will focus on a specific class of memory devices – targeted to mobile and IoT applications – that use “SPI” (Serial Peripheral Interface) signaling. SPI was developed by Motorola… Designing with Silvaco’s Octal SPI Memory Controller with Advanced Memory Support for IoT Systems

-

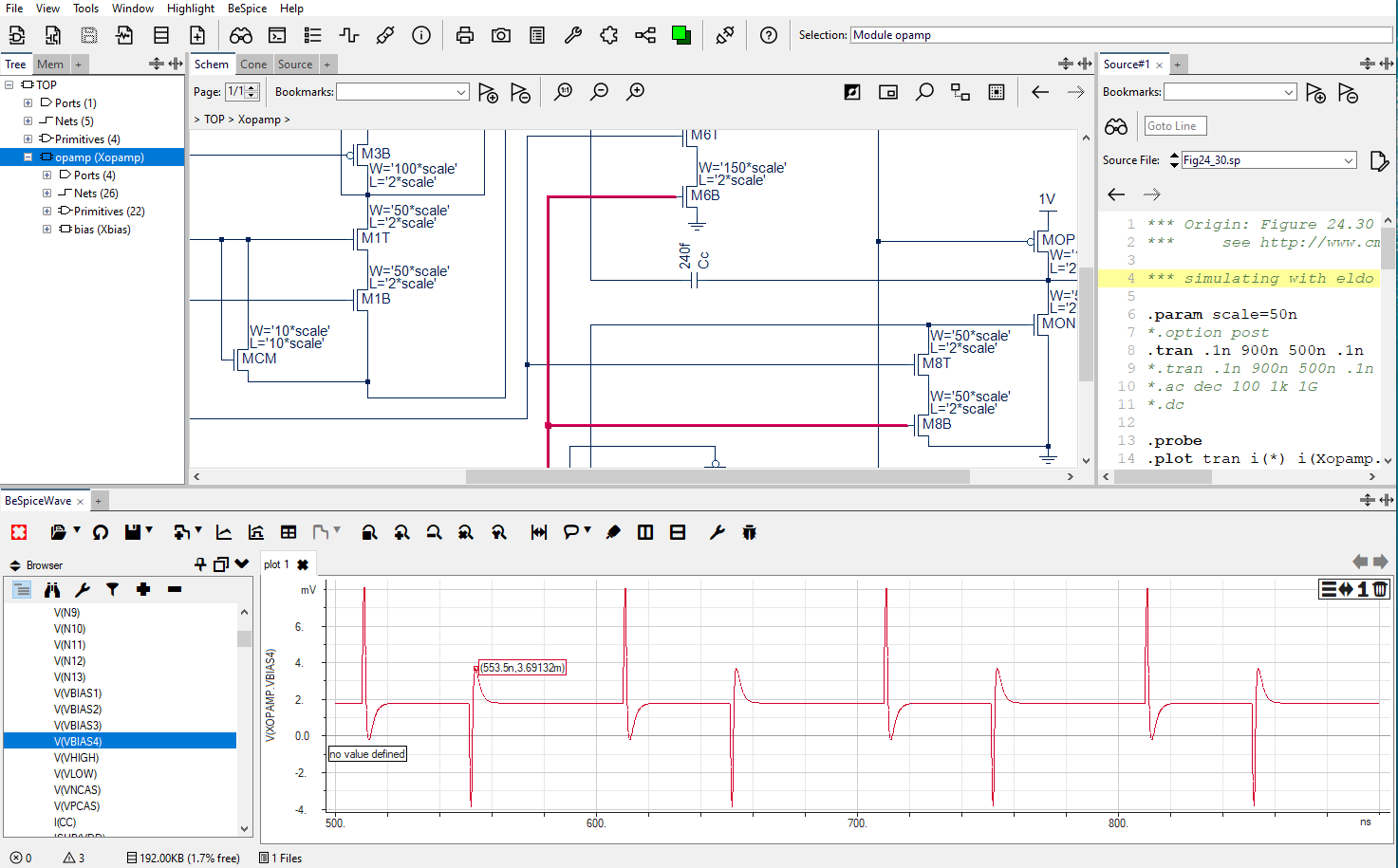

Analog Waveform Viewing with Schematic Cross-Probing

Debugging takes a significant proportion of any engineer’s time, and there is much that can be done to improve individual and team’s productivity in this area. Using SpiceVison PRO and it’s analog waveform capabilities, users can perform post-processing functionalities and perform various measurements. Make SpiceVision PRO your unified platform for viewing and debugging analog circuits.… Analog Waveform Viewing with Schematic Cross-Probing

-

UVM for FPGAs (Part 1)

Presenter: Srinivasan Venkataramanan, Entrepreneur and Head of VerifWorks Thursday, September 9, 2021 Abstract: The Accelera Universal Verification Methodology (UVM) became an IEEE standard published as IEEE 1800.2 – IEEE Standard for UVM Language Reference Manual (LRM). UVM has been the predominant verification methodology for ASIC designs for many years and has recently gained popularity and… UVM for FPGAs (Part 1)

-

AI Hardware Summit

AI Hardware is evolving – and so are we! As machine learning models continue to grow in size and complexity, and more and more models enter production in enterprises worldwide, the way we approach accelerating these workloads is changing. At the front end, data-centricity is taking precedence over model-centricity. At the back end, AI practitioners… AI Hardware Summit

-

Methodics User Group

Our customers are always coming to us with great questions, and in response discovering unique solutions, but we’ve never had a forum to share these learnings to our wider customer base. I've been considering a forum for discussing best practices for a while and, now that we're part of the Perforce family, we have the… Methodics User Group

-

Improving Initial RTL Quality

Development projects, whether FPGA or ASIC SoCs or IP, run into late surprises that quickly result in schedule slips, expensive rework, and/or difficult feature cuts. It is possible to find entire classes of issues without waiting for a testbench. This webinar will introduce you to a testbench-free designer-driven verification flow, resulting in a lower cost… Improving Initial RTL Quality

-

How Synopsys Interface IP and Arm Interoperate to Accelerate System IO and Memory Performance

In this webinar, Synopsys and Arm describe how their recent collaboration helps maximize system performance and shorten Arm-based SoC design cycles. Learn how to minimize HPC/data center SoC design risk and ensure end-to-end IP integration, using available Arm reference designs and interoperability reports. Find out how Synopsys’ interface IP for the most widely used protocols… How Synopsys Interface IP and Arm Interoperate to Accelerate System IO and Memory Performance

-

GF Technology Summit 2021

DELIVERING A NEW ERA OF MORE Semiconductor chips are pervasive—inside everything from appliances to thermostats, smartphones to automobiles, and industrial equipment to medical devices. These incredibly complex feats of human ingenuity power our world, fuel the global economy and enrich our lives. The GF Technology Summit offers an opportunity to discuss the challenges and opportunities in semiconductor design and… GF Technology Summit 2021

-

Automatic Generation of SystemVerilog Models from Analog/Mixed-Signal Circuits: a Pipelined ADC Example

When verifying large SoC designs, one needs to write SystemVerilog models for analog/mixed-signal blocks to comply with the digital verification flow, such as UVM. This talk addresses ways to extract those models automatically from circuits. The first approach is called structural modeling, mapping each device in the circuit to an equivalent model in SystemVerilog and… Automatic Generation of SystemVerilog Models from Analog/Mixed-Signal Circuits: a Pipelined ADC Example

-

How to Improve Your Chip Design Performance and Productivity Using Machine Learning

New applications and technology are driving demand for even more compute power and functionality in the devices we use every day. This has resulted in the semiconductor industry experiencing strong growth based on technology like 5G, autonomous driving, hyperscale compute, industrial IoT, and many others. System-on-chip (SoC) designs are quickly migrating to new process nodes… How to Improve Your Chip Design Performance and Productivity Using Machine Learning

-

Benefits of a Common Methodology for Emulation and Prototyping

Overview Many design teams have used some form of hardware verification throughout their verification cycle for years now. Some engineering teams prefer to use emulation, some prefer to use prototyping, and some even use both. Why would engineering teams invest in both platforms? Join our experts to understand why you should consider bridging emulation and… Benefits of a Common Methodology for Emulation and Prototyping

12 events found.