FPGA

Events

-

-

FPGA Design Verification – Planning

As FPGA technology continues to evolve - to provide us with full-blown SoCs with CPU, GPU, and high-speed peripherals, for example, joining the traditional programmable logic area - design verification becomes increasingly challenging. Lab-based FPGA testing and bring-up alone are clearly insufficient, especially for safety-critical designs, and FPGA teams are adopting advanced design verification methodologies…

-

FPGAworld Conference 2023 – Stockholm

ÅF Frösundaleden 2A, 169 70 Solna, SwedenThe FPGAworld Conference is an international forum for researchers, engineers, teachers, students, and hackers. It covers topics such as complex analog/digital/software FPGA SoC systems, FPGA/ASIC-based products, educational & industrial cases, and more. Registration for attendees is free and includes 2*coffee, lunch and go-home drink. Keynote Speaker Copenhagen and Stockholm 2023 Keynote speaker: Martin Kellermann , Microchip…

-

FPGAworld Conference 2023 – Copenhagen

DTU Science Park 2800 Kongens, Lyngby, DenmarkThe FPGAworld Conference is an international forum for researchers, engineers, teachers, students, and hackers. It covers topics such as complex analog/digital/software FPGA SoC systems, FPGA/ASIC-based products, educational & industrial cases, and more. Registration for attendees is free and includes 2*coffee, lunch and go-home drink.

-

Maximize Design Productivity using Vivado ML with SystemVerilog

Although SystemVerilog is perhaps most widely used in the context of hardware verification, it also contains many features directly relevant to FPGA hardware designers. We explore the features of SystemVerilog that are useful for RTL synthesis using Vivado™ ML Editions from AMD, showing how the RTL SystemVerilog language constructs have been optimized for productivity and reliability.…

-

FPGA Design Verification – Advanced Testbench Implementation

Abstract As FPGA technology continues to evolve - to provide us with full-blown SoCs with CPU, GPU, and high-speed peripherals, for example, joining the traditional programmable logic area - design verification becomes increasingly challenging. Lab-based FPGA testing and bring-up alone are clearly insufficient, especially for safety-critical designs, and FPGA teams are adopting advanced design verification…

-

-

FPGA Design Verification – Advanced Methods

Abstract As FPGA technology continues to evolve - to provide us with full-blown SoCs with CPU, GPU, and high-speed peripherals, for example, joining the traditional programmable logic area - design verification becomes increasingly challenging. Lab-based FPGA testing and bring-up alone are clearly insufficient, especially for safety-critical designs, and FPGA teams are adopting advanced design verification…

-

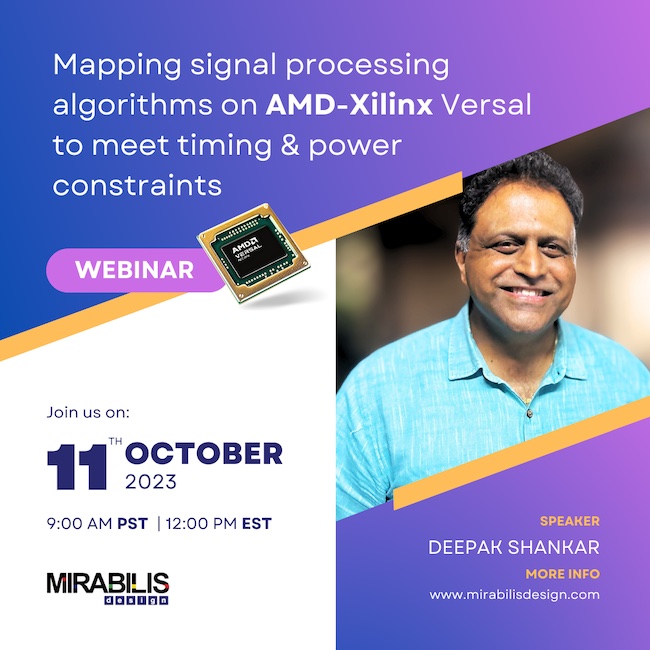

Mapping signal processing algorithms on AMD-Xilinx Versal to meet timing and power constraints

In this Webinar, we will focus on the performance-power-area trade-off in implementing signal processing algorithms on Xilinx FPGA by partitioning the tasks of the algorithms onto the processors, logic and AI Engines resident in the AMD-Xilinx Versal FPGA. Key Takeaways: Discover the inner workings of FPGA components: Processor, Logic Elements, AIE/Tensor, and more. Understand latency…

-

High Reliability and Functional Safety Applications for FPGA

When designing any new system, safety and reliability are key factors in determining if a system is safe for real-world deployment and if there are sufficient contingency plans for worst case scenarios. This is no different for the designs targeted for FPGAs based deployments. Today, FPGA based designs are utilized in many safety critical systems in the…

-

-

CHIPS Alliance – FuseSOC: Package manager and build abstraction tool for FPGA/ASIC development

Google 237 Moffett Park Drive, Sunnyvale, CA, United StatesIP share and reuse is fundamental for efficient chip design. But in order to do this efficiently we need tools and methods. On the software side, the concept of package managers is widely used to build a product from many different sources, but chip designers often rely on ad-hoc solutions which tends to build up…

-

FPGA Frontrunner Meet & Greet

Thales 350 Longwater Avenue, Reading, United KingdomThe FPGA Front Runners event will be hosted by Thales at their venue in Reading. The event will focus on “Security at System Level, and what security features we need in our FPGA to support this”. If you are interested in speaking at this event please email mike.bartley@techworks.org.uk Topics for talks: What is Security in FPGA-based…

-

-

FPGA Forum 2024 – Norway

Royal Garden Trondheim, NorwayFPGA-forum is a yearly event for the Norwegian FPGA community. FPGA-designers, project managers, technical managers, researchers, final year students and the major vendors gather for a two-day focus on FPGA. There will be presentations from the Norwegian industry about methodology and practical experience, – the universities will present new and exciting projects, and the vendors…

-

-

High-Performance RTL Simulation Workflow with Vivado and Active-HDL

Based on recent industry research, the FPGA market was valued at approximately USD 7.5 Billion in 2023, with an expected compound annual growth rate (CAGR) of around 10% by 2032. More and more engineers will be adopting FPGAs due to their versatility, acceleration capability, power efficiency and lower non-recurring engineering (NRE) costs (compared to ASICs).…