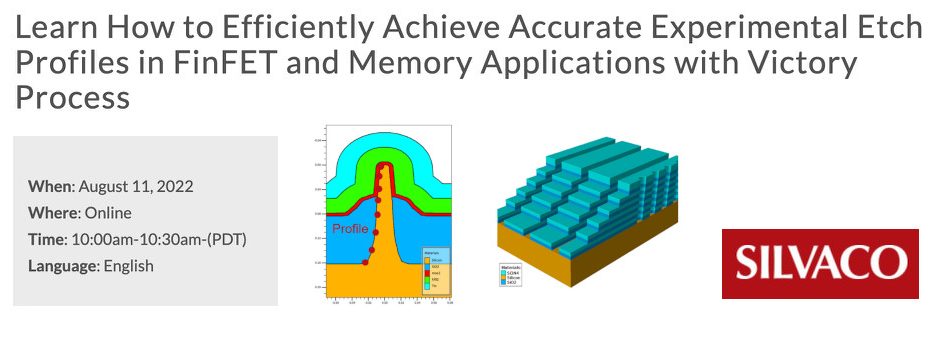

Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

When employing process simulation to generate a complex device structure, TCAD engineers often face the task of reproducing the exact etch profile that has been observed in semiconductor fabrication. Silvaco Victory Process offers several geometric…