On Tuesday I had a Suite presentation from Jerome Toublanc, Principal Product Engineer at Apache.

On Tuesday I had a Suite presentation from Jerome Toublanc, Principal Product Engineer at Apache.

They are a private growing company founded in 2003 with a focus on power and noise integrity for chips, SIPs and packages.

Products Include

– RedHawk – SoC Power (dynamic voltage drop) Chip Power Model (8 0f 20 top semi clients)

– Sentinel (Optimal) – package/pcb power (13 of 20 top semi clients)

– Totem (new this year), analog IP power, transistor level (18 0f 20 top semi clients)

Worldwide the company hs: 100+ customers, 160 people, 50% R&D (Asia, Japan, Taiwan) , HQ in Valley.

Chip-package-system design risks are:

IP power, substrate noise

Chip Fmax

IO DDR jitter

EMC requirements at board level

The Value to solve these risks are:

Reduce costs (fewer board decoupling caps, number of package layers, signal pads to power pad ratio, area of IP blocks)

Tools offered by Apache are:

SOC – cell-based, Redhawk (LEF, DEF)

Create Chip Power Model (CPM) for use in Sentinel. Spiced-based model, open, current source and L.

Totem – transistor-level for IO, memory, full custom IC.

Create a macro-model for use in Redhawk

Sentinel – Package levels (Create RLCK or s-parameters for use in Redhawk)

The tool usage used to be just at tape-out, is my design OK for IR drop? Now the usage is during P&R or floor planning let’s do an IR drop analysis.

Requirements for noise analysis are:

Capacity – billion transistors full-chip

Accuracy – on-die inductance of power grids

Smart – no vectors, not depending on input stimulus

Packaging – the full package, using a field solver.

Chip Package System (CPS) – co-design needed, both frequency and time-based

Optimal was a 2.5D field solver, now the technology is full wave 3D solver

Redhawk -(competes with VoltageStorm/CDN) pdn prototyping, dynamic voltage drops, low power design verification, die model creation, impact on timing, power/signal EM. I know my IR drop, now the impact on clock timing.

– First release was SDL in 2003, single core cpu, flat designs, lumped RLC package, sign-off use, voltage island, clock gating. 90nm

– EV release in 2006, multi-core (2), caching, distributed RLCK package, prototype usage, MTCMOS, 65nm

– NX release in 2009, pattern matching, hierarchy, multi-port s-params for package, root cause identification, LDO switched RAM (45nm, 32nm)

Capacity of Redhawk:

2005, 60m nodes

2006, 142M nodes

2008, 400M nodes

2009, 751M nodes, use a 64 bit CPU

Redhawk GUI: intuitive IR drop highlighting looks like a web browser (Tcl/TK interface), text values with click to visualize resistance, length, IR drop

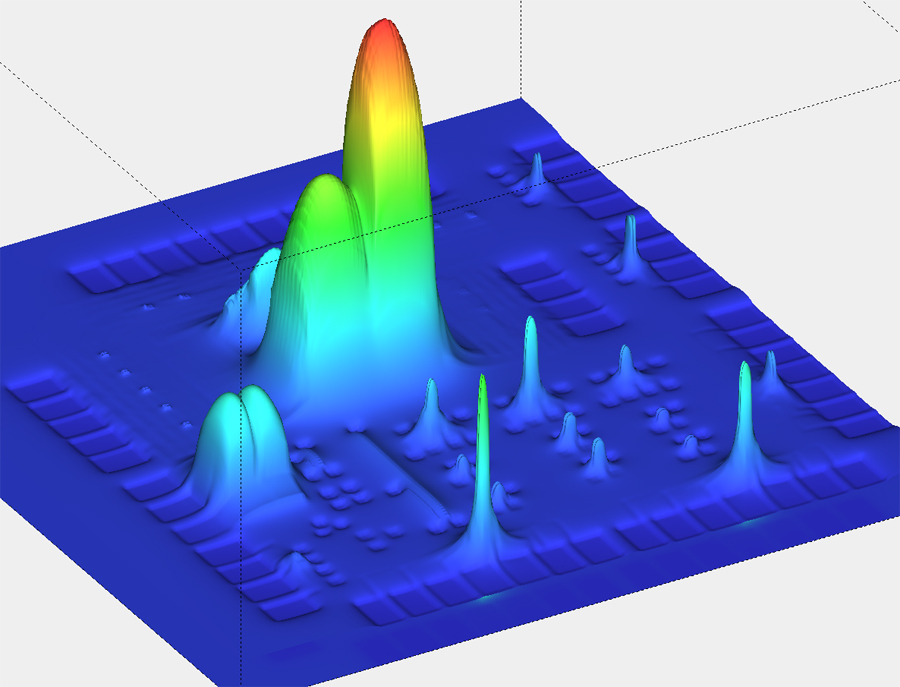

Totem – analog and full custom IC designs, transistor-level approach

– Grid weaknesses, power / signal em, static /dynamic ir, substrate noise, model creation

– Could run SPICE to see IR drop but you don’t see the GUI and colors

– Capacity of 100M devices in <12 hours simulation time

– Static and dynamic analyses

– Accuracy: power/ground, substrate, package concurrent, silicon measurement correlated (use own spice simulator: HSPICE, XA, Eldo, Spectre), simulate p/g grid with current sources

– Accuracy in white paper on the web

– Use the Open Access (OA)

Sentinel – package and board focus (extraction required)

– Use CPM model for each chip

– Size the pdn

– Signal integrity

– EMI/EMC for auto designers

– Thermal design

Models – Chip (power model, IO model, emission model, thermal model)

3D Full-wave extraction – packages, Fast FEM (FFEM) for full package and board together

– Integrated co-simulation of AC, DC, transient

Sentinel – SSO, EMI, Thermal,

Customer demos: Broadcom, rambus, tsmc, st, kobe u, cisco systems

Q: Models at 40nm or 28nm?

A: Yes, give us the layout info for each layer.

In summary – I see Apache as one of the brightest pre-IPO EDA companies in the industry because of their product focus and growth during a recession.

[…] Apache has created a handful of power and signal integrity point tools, and this acquisition will help them broaden their tool suite to include a Design For Power flow. I wrote favorably about Apache at DAC. […]