1) Megasolvers – These help out on large designs allowing up to 10 million elements to be simulated at SPICE accuracy on a 64 bit CPU.

2) Multi-core – Now supported and it give you about a 2X run time improvement using 4 cores. In the token-based licensing 1 token simulates up to 50K elements, 2 tokens up to 500K elements and 3 tokens is unlimited elements. If you are simulating on a single core then you’ll see a note of how much speed-up is possible with multi-core.

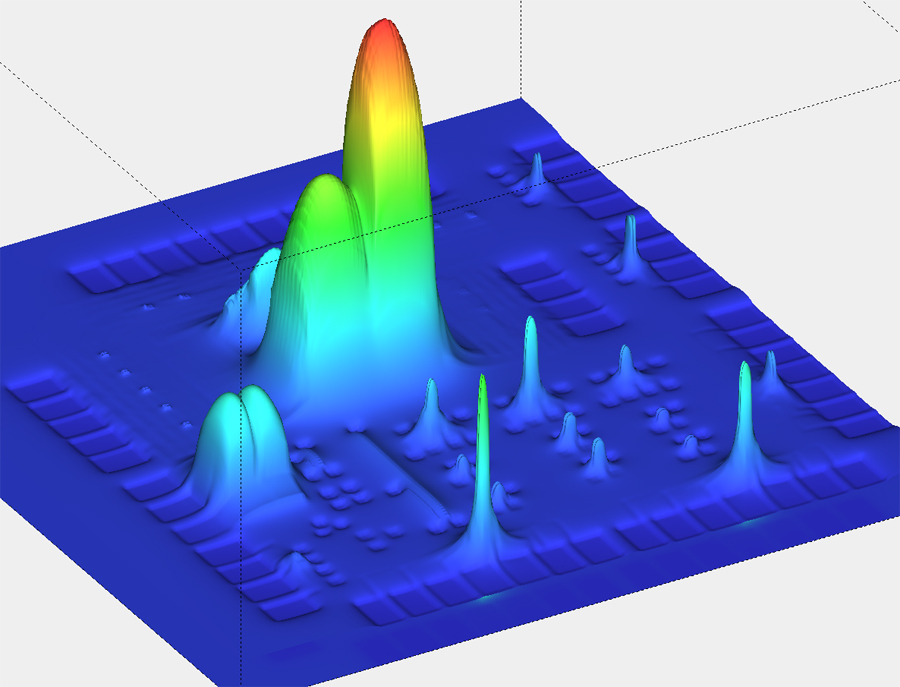

3) Device noise analysis – True SPICE accuracy for all block styles and it’s especially useful for 90nm and below nodes, 1v and below supplies, on PLL and analog or RF circuits.

The modular architecture at BDA yields a simulator family with a single executable. You can even co-simulate with and HDL simulator using the Verilog API.

Earlier this year they announced a lite version of their tool called AFS Nano which works on smaller designs up to 5K elements and has entry-level pricing of just $1900 annually. This is a real bargain for designers with lots of smaller designs for simulation.

Cadence disconnected BDA from the Connections program which is really quite unfair but understandible because of the direct competition in the SPICE segement.

TSMC has certified the BDA simulators down to the 40nm node, and they are serving 15 of the top 20 semiconductor companies in the world.

Software-based circuit simulation is the future and GPU-based simulation is not really worth it.

This 40 person company seems to be well focused on the analog circuit simulation segment, offers innovative pricing and has no plans to be acquired. Check out their technical paper at DAC, “A Robust and Efficient Harmonic Balance Using Direct Solution of HB Jacobian.”

Well done on winning the DAC best paper award:

A Robust and Efficient Harmonic Balance (HB) Using Direct Solution of HB Jacobian”

Amit Mehrotra – Berkeley Design Automation, Inc., Santa Clara, Calif.

Abhishek Somani – Berkeley Design Automation, Inc., Bangalore, India