On Tuesday I spoke with Chi-Ping Hsu, Senior VP of R&D for the Implementation Products Group about the direction that R&D is headed at Cadence. In 75 minutes we covered 52 corporate slides and I quickly sensed that Chi-Ping is genuinely excited to be at Cadence and leading his troops forward in the highly competitive IC tools market.

Half of all R&D at Cadence reports into Mr. Hsu yet he’s also done stints at start-ups like Get2Chip and Pie. Most of us have heard about the Power Forward Initiative, a program that he started back in 2005. Here’s the list of participating companies:

For competitive reasons we don’t see Mentor or Synopsys as part of this coalition but that’s they way most of EDA history has worked out.

I learned that Cadence spends the most in EDA on R&D even ahead of Synopsys. There are about 2,200 total R&D people at the company.

Major product releases are done annually while intermediate releases come out about once every 3 months, it depends on how new the tool is. Skill code is still very important and fully supported for the analog and transistor-level tools, along with Tcl-based tools in the digital product line.

All of the acquired point-tool products have been integrated into a unified flow and support the OpenAccess API. They now offer common technology for: timing, extraction, power, SI, DFM.

Morale is good even after the down-sizing to get more fit financially. Former architects have rejoined the company because they like the new direction.

On the logic synthesis side the Get2chip technology (Encounter RTL Compiler) is well received with 450 customers using it. The Conformal tool for logical equivalency checking has a 70% market share

Even well-known point-tool providers in the static and dynamic IR drop segment like Apache are loosing benchmarks and seats to the Encounter Power System.

Each R&D group creates and monitors a 5 year plan in order to identify the technology trends and then they create or acquire tools to meet the challenges.

With feature-rich EDA tools it was interesting to hear that a recent survey at Cadence found that many tool users were comfortable using only 10% of the features. The Metrics-driven Productivity Initiative started 6 months ago will address how to make customers more productive with the tools that they already have. Many clients are now seeing a 30% productivity improvement by just learning how to use features that are new to them along with the best methodology.

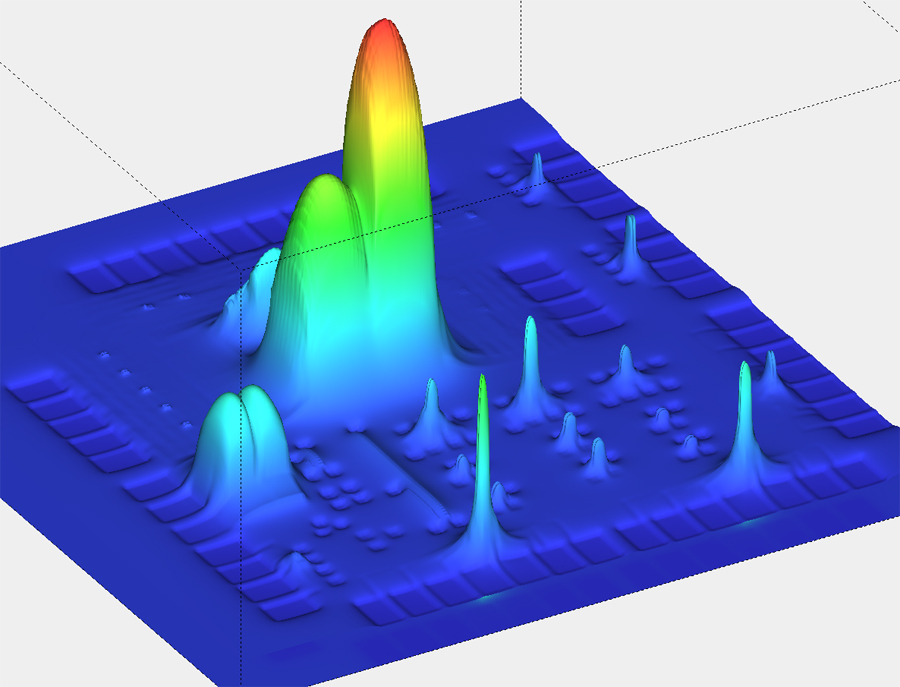

Another initiative is called GGI – which stands for Gigahertz, Gigagates Initiative. How do you design these huge SOCs that can be built in 32nm and smaller nodes? The marketing name for the tools is called Encounter Digital Implementation, or EDI.

I asked about GPUs being used to help speed up run-times for compute intensive tools. The reply was, “It’s under study.”

In summary I’d say that Cadence has a clear vision to be leaders in analog, mixed-signal, low-power and verification. This could be the new Cadence rising by being aggressive, taking risks and having close customer contact.