On July 16th I met with three Cadence people in Oregon to get an update on the Virtuoso product line, the leading IC layout and design environment in EDA:

- John Stabenow, Marketing Group Director, Virtuoso Platform

- David Desharnais, Group Director, Product Management

- Jeff Berry, AE

Q: Where does Virtuoso fit into EDA360?

A: Virtuoso is part of the Silicon Realization (SOC and System Realization are the other two pieces of EDA360).

Q: Do you support the OASIS format?

A: Yes, as of release 6.1.5

Q: How often do you release Virtuoso?

A: From release 6.13 to 6.14 it was about 18 months. In between we have Incremental Software Releases.

Q: How are competitors doing against Virtuoso?

A: Most of them are merely cloning Virtuoso v5.1, while we’ve added significant features in the 6.1 releases.

Q: What’s the vision for Silicon Realization?

A: Create and integrate, concurrently both top down and bottom up.

Q: How many people does Cadence have working on Virtuoso?

A: 800 engineers on custom analog, IC layout, simulation, schematic, environment, routing, drc, lvs, electrical sign-off, OPC, Spectre, APS, UltraSim. 400 engineers on Virtuoso split between front and back end.

Q: Is Open Access open source?

A: No, it’s an open standard through Si2.

Q: How much more productive are Virtuoso 5.1 to 6.1 users?

A: We’ve measured on average an improvement of 30% when using the new features. We can actually measure this based on metrics-driven productivity, things like how many clicks does it take to get a task done, logging keystrokes to see what is repeated and why.

Q: What happened to Q-Design technology?

A: It’s now integrated in Virtuoso and called Layout Migrate. This competes with Sagantec tools.

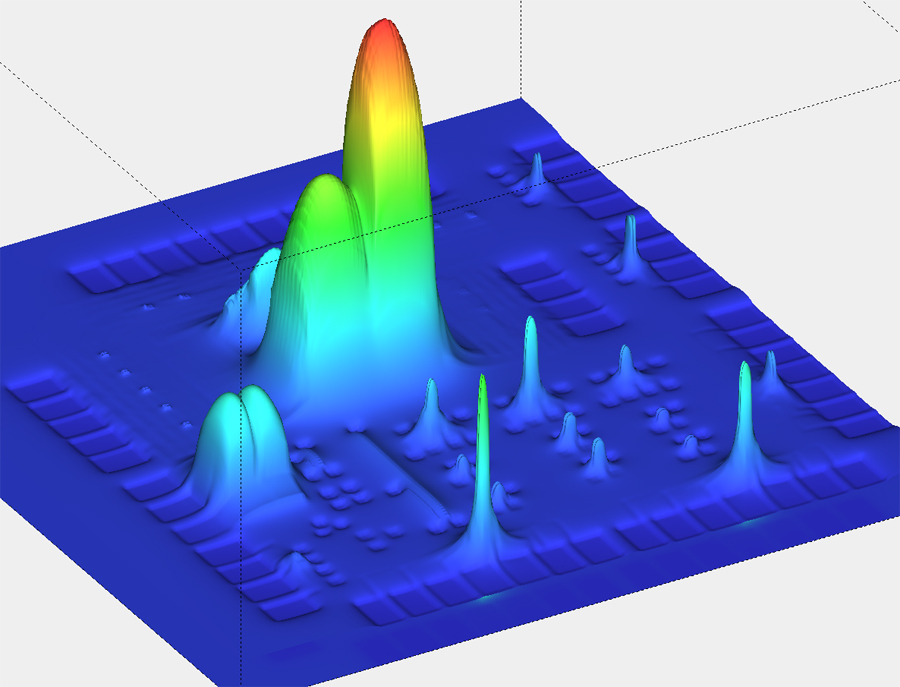

Q: Where’s the Neolinear optimization?

A: We integrated that years ago, and it’s native now.

Q: What are some of the methodology issues that limit IC layout productivity?

A: Having teams with separate front-end and back-end people. You need an automated way to pass constraints for the circuit designer on the front-end to the layout designer on the back-end. Even floorplanning constraints can be set by the circuit designer.

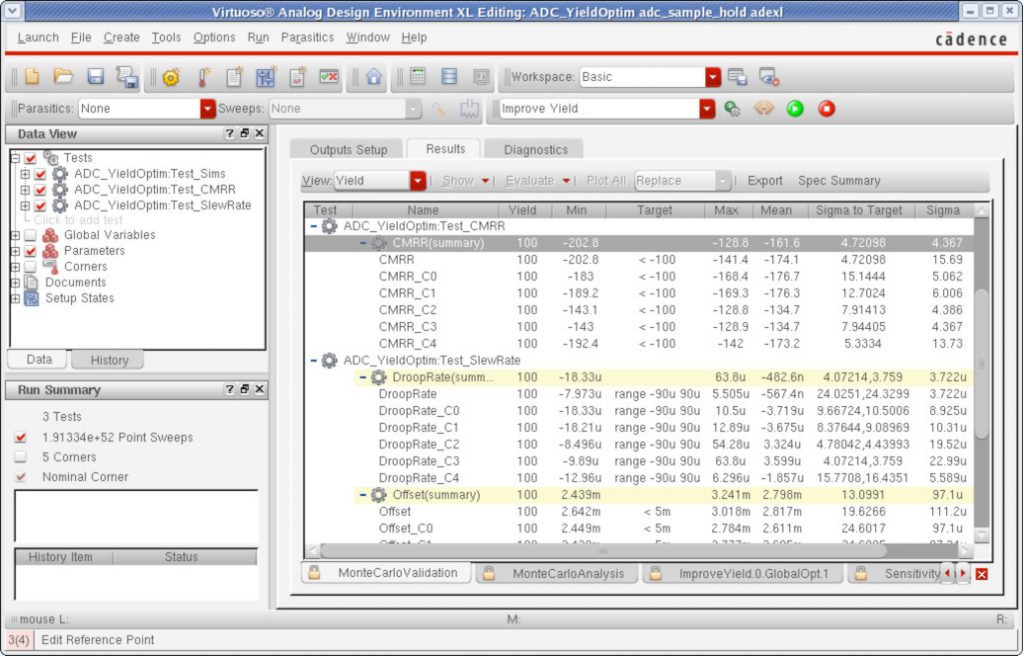

Q: The digital designers have a very automated process for simulation and verification. What do you offer the analog designer?

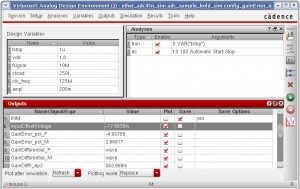

A: In the Analog Design Environment with XL you can re-use your setup and test benches.

Q: How is Virtuoso aware of manufacturing issues?

A: You can find DFM issues, report them in Virtuoso, recommend fixes, use migration tools for compaction, and even use auto-fix.

Q: How would I manage my circuit simulations?

A: In our circuit design environment you can manage a large amount of tests, like: Monte Carlo, intelligent corners, design centering, design optimization, etc.

Q: What kind of reliability simulation do you offer?

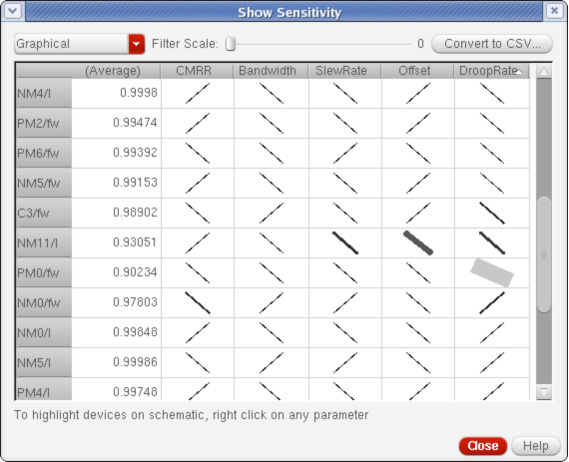

A: You can simulate aging, define stress tests, test harness, device performance, circuit sensitivity and worst case analysis. For yield issues – statistical effects, well proximity and stress effects.

Q: Can you streamline my design reviews?

A: Yes, we have something called auto documentation in ADXL.

Q: How do I get parasitic info into my analog simulations?

A: We have rapid prototyping from schematic into layout so that you can quickly see the effects of parasitics.

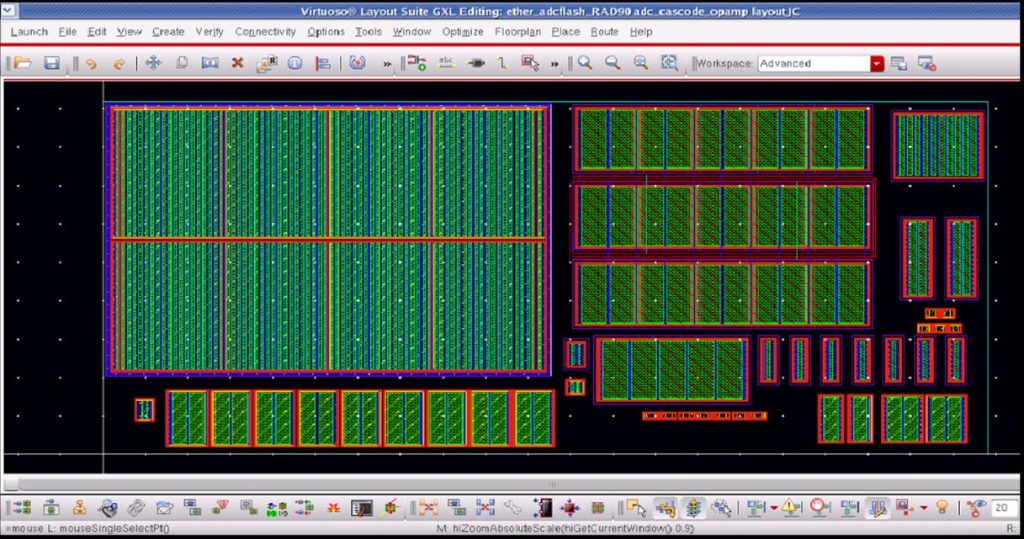

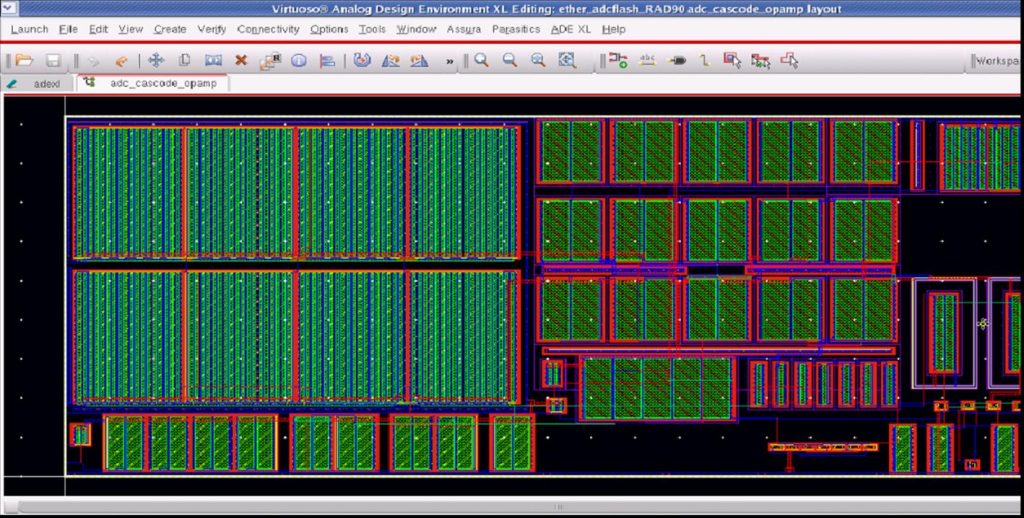

I saw a video demo where an Op Amp schematic and layout were created, simulated, optimized, placed, routed, extracted and verified. Pcells and Modgen were used.

Q: How do I learn Virtuoso?

A: You could attend a workshop, read a tutorial, or video about 80 videos.

Q: What’s coming up?

A: A new waveform viewer called VIVA and improvements in analog routing.

Summary

I learned that Cadence offers IC tools and flows for the traditional design team with circuit designers and layout designers (instead of replacing layout designers) that need to collaborate. They continue to innovate, add new features, measure improvements and are the incumbent EDA vendor for full-custom IC design world wide.

Competitors are nipping at the heels of Cadence by offering compatibility with the OA database and then adding interoperable PDKs. Cadence counters by supporting Open PDK. Others argue that iPDK and Open PDK are complementary approaches to Process Design Kits.

very nice summary of the new features in Virtuoso. Is the video you saw on the OpAMP available from Cadence’s WEB site? If so, a link?

Steve,

Good point, I’ll ask and find out.. stay tuned.

Daniel

Good to see Cadence is resuscitating Virtuoso and all applicable accessories. Sadly they still seem to be just catching up with many of new capabilities introduced by some of the little guys. They also don’t seem focused on the next paradigm shift for greater productivity. I’m really impressed with Magma Titan stuff – really a whole new way to tackle analog design and much (10x) faster than Cadence way. Only dings

– Magma doesn’t do native OA so interoperability is a little painful.

– They need to do a better job interfacing to HSPICE

Additional win – works with the same IPL PDK as SpringSoft, Synopsys, etc.

David,

Cadence is certainly not resting on their laurels with Virtuoso.

The Magma Titan approach of using equations as input to optimization is novel and fast, while the old school optimization methods are rather brute-force simulation based.

Magma wants to sell more FineSIM so they have less desire to make the best interface to HSIM in spite of the dominance of HSIM in the market place.