I met with Dave Milman, Marketing at Ciranova on Tuesday afternoon.

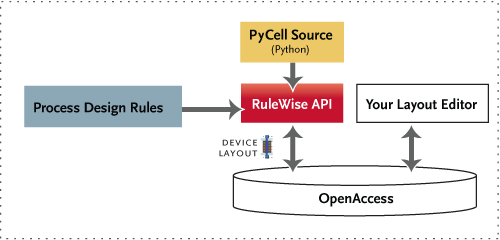

Big news this last week is that TSMC is now supporting iPDKs because we are no longer locked to Cadence Pcells. PDKs from foundry supported Pcells, but then each EDA company supported their own PDKs. Now any layout editor can use iPDKs. Many different tools can be used for IC design in a foundry flow.

Pycells – free technology, IPL Alliance, free software but not open source, write Pcells, cannot resell Pycell Studio.

Analog design – it’s all about the devices so Pycells have all the devices that you can imagine.

Pycell Studio – free software with thousands of downloads so far from hundreds of different companies.

Cadence, Springsoft, Synospsys,, Mentor Calibre – all are using the OA api.

Helix – used by analog designers, design groups doing layout. Reference customers coming soon. Commercial use for two years now and tapeouts in progress. The bigger the analog block the bigger the need, big SOC guys (cell phones, RF, transceiver, serial channels). Time -based license, network tool, one license can serve a group of multiple. Both circuit people and layout designers can use Helix (80% or more by layout designers, some 20% it’s the circuit designer).

– Start with a netlist, now we see unconstrained layout, Helix can understand hierarchy and connectivity, start area estimates (no effort), start to constrain the layout (ins on left, outs on right), couple rows and columns. Simple to learn.

– Many years we’ve seen SDL in tools.

– Helix does APR.

– First five customers are driving the tool feature list.

– Complex rules for correct-by-construction results, support three types of wells. Abutted cells, intelligent.

– Virtuoso is also smart about libraries and features, device abutment.

– Automation tool needs to know how to abut and merge, then design rule correct. Abut without a contact inbetween.

– Add a contact between abutted poly,

– Different widths abutted (devices supported, and tools too)

Helix GUI – add two devices to a row, then add rows to a column, creates a text file

– Other tools can create this command file

Today – flow: virtuosos ADE, calibre, HSPICE, all used in a different way. Don’t restrict the flow, let them use it their own way.

Live demo – PLL design, netlist, no constraints, APR for transistor-level designs in under a minute

– Uses netlist, PDK, tech file

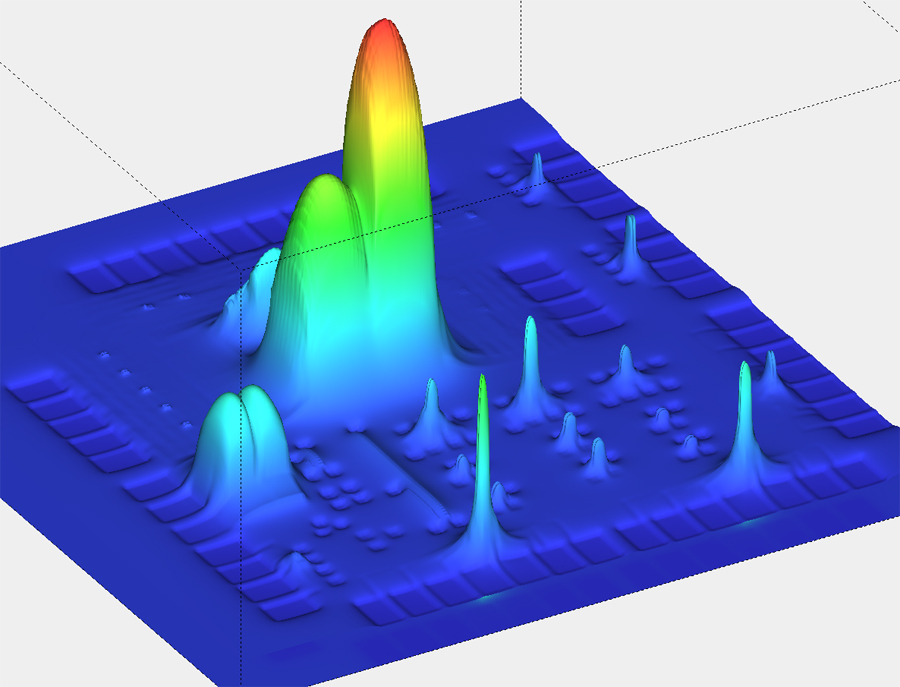

– Helix does analog APR, curve of all layout space choices (width versus height)

– Easy to use out of the box

– Want inverters placed in symmetrical order (add some constraints) – about a minute of constraints on VCO

– Defined Ins on Left, Outs on Right, use some rows

– 2nd pass add constraints to match P and N devices in matched and mirrored layout, add guard rings

– All the layout is DRC correct by construction (Flipping, mirroring)

– Results after 2 constraint sessions: matching, mirroring. Finds lots of layout solutions to find optimal layouts, expert exploration results

– With about an hour or two of constraints: results look hand-crafted

– Constraint changes to move Inputs/Outputs: (running on 8 core Linux machine)

– Other designs: 24K devices, 40 cpu minutes on 4 CPU. 50K devices, 30cpu minutes on 8 cpu.

– Trial Router: fast and with parasitic

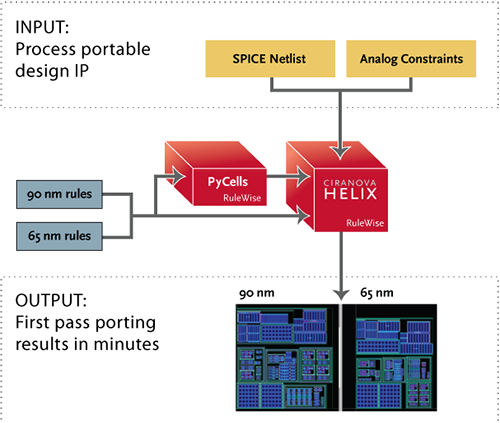

– Constraints can be used to a new process

– Move IP to new node: 130nm to 65nm example, same schematic, re-use constraints, new tech file, same PDK w new tech file (makes it process portable, removes layout from bottleneck)

– Benefits: cut 50-80% analog layout time, floodplan entire design at once, get to an extracted state easily,m

In summary I see Ciranova as one of the most sophisticated IC layout automation tools available that is easily used by either a layout designer or a circuit designer doing full-custom ICs. After our talk and demo an un-named customer from a popular microprocessor company walked up to the booth, so I see a very bright future ahead for Ciranova.

Interesting how fast these bots republish my blog post.

It’s too bad you didn’t make it by our booth [Analog Rails] for a demo, especially with your summary conclusion as seeing “Ciranova as one of the most sophisticated IC layout automation tools available”

Our product blows them out of the water both in features and scope. We are best in class by a wide margin in analog and made huge strides this year by implementing mixed flow.

Check out our website for an overview, but you need to see it in action to understand the game-changing work we have performed. Have you been in contact with Cliff?