At the 2009 DAC I was visiting Ciranova at their booth when an Intel guy walked up and started talking excitedly with an executive about using Ciranova tools, at which point the executive asked me to ignore what was happening in front of my eyes. I honored the request and didn’t mention it in my blog until today because there was a new press release about Intel Capital investing in Ciranova. When was the last time that we heard of an EDA company receiving funding? It’s been too long.

I’m delighted to see that Intel is investing in new EDA companies and it kind of hints that perhaps the big four established EDA companies are under-serving the transistor-level IC layout market place.

In the old days the transistor-level circuit designers would throw their netlists over the wall and then the layout group would pick it up, do a layout, and throw it back over the wall. This implies a certain number of iterations and some inefficiency.

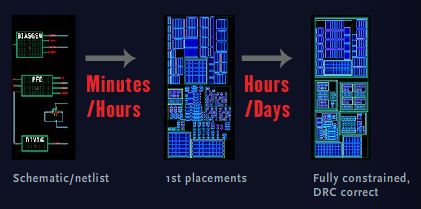

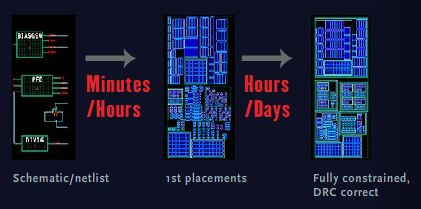

Ciranova simply places a lot of layout automation power in the hands of the circuit designer so that they can get decent layouts quickly, then do simulations and tweaks without needing as many layout people.

Ciranova Helix

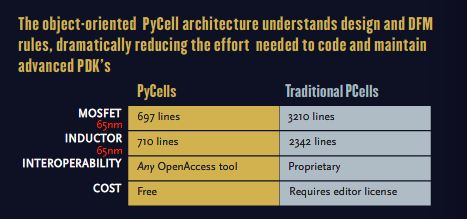

The other innovation that Ciranova offers is a more efficient way to write analog or digital cells using the Python language:

Ciranova PyCells

To deal with the installed base of Cadence Virtuoso users the folks at Ciranova have figured out how to use the OA database and co-exist with Cadence SKILL PCells.

This classic strategy of embracing the de-facto standard and then extending it is a winner for Ciranova and the IC industry as a whole.

Getting investment in the company is certainly good, but it could never replace paying, happy customers. Otherwise we are back to 1999.