Last Friday I had an online meeting with Ashutosh Mauskar, vice president of Magma’s Custom Design Business Unit to learn what was new with the Titan product lineup.

Last Friday I had an online meeting with Ashutosh Mauskar, vice president of Magma’s Custom Design Business Unit to learn what was new with the Titan product lineup.

Magma has been very involved with interoperable PDK libraries, or IPL so that IC designers with analog and mixed-signal projects can mix and match tools to implement their chips.

Magma has been very involved with interoperable PDK libraries, or IPL so that IC designers with analog and mixed-signal projects can mix and match tools to implement their chips.

At DAC this year Magma was the chartered sponsor for the IPL lunch, very active with TSMC, Synopsys, CiraNova. Together they create and validate IPL interoperability.

Titan is the platform and has lots of tools: Schematics, Layout, Analog Simulation Environment, Schematic Driven layout, Shape based router (different). Analog Design Accelerator: Analog Circuit Accelerator (ACX), Analog Virtual Prototyping (AVP).

OpenAccess (OA) is fully supported providing a unified electrical, physical and verification database. Cadence created OA and ironically it allows competitors like Magma to win seats at Cadence accounts.

Titan Analog Simulation Environment is new this year and gives you an integrated environment to view waveforms, make measurements (Jitter Analyzer, FFT/SNR Analyzer, INL/DNL Analyzer and AC/CD Analyzer) and launch circuit simulators like FineSim SPICE and FineSim PRO. The only thing missing from FineSim PRO is handling hierarchy for simulating RAM blocks and tight co-simulation with VHDL and Verilog.

Titan Schematic Driven Layout is another new capability offered this year. SDL tools have been around for years, so there was a bit of catch-up here.

TSMC has certified the entire flow of Magma Titan tools for iPDK use.

The Titan Shape Based Router now has several tape-outs, works on Analog Blocks and connects to digital for finishing and chip assembly. This router looks sophisticated and capable.

Geeks will enjoy using the Tcl command line to automate repetitive tasks and add new automation, plus automating full chip assembly.

Clients – stay tuned for names in a future press release.

Performance on the largest IC designs was impressive. One table showed multi-gigabyte designs being loaded in just minutes.

The strategy for analog tools is: be open, standards-based and provide a full set of tools.

The most elegant part of the Titan lineup is what they call Analog Design Accelerators (ADX).

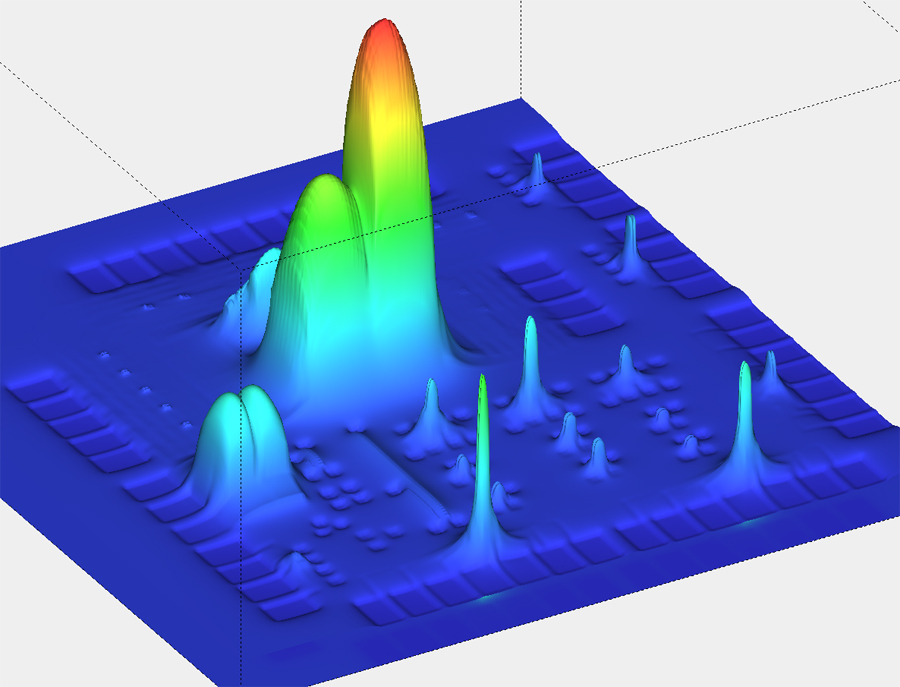

Technology from Sabio Labs is now called Analog Circuit Accelerator (ACX. You describe your analog or mixed-signal design in Matlab format (or use a provided library), provide a netlist and constraints, then their tool optimizes your transistor sizes to meet your constraints. This optimization is not simulation-based, rather it is equation-based. Instead of launching 10,000 SPICE runs the optimizer solves equations in a fraction of the run-time. Now that’s elegant.

The precursor to Sabio Labs approach was a technology used by Barcelona Design, based on a proprietary language called Flamingo that couldn’t even be simulated. Full disclosure – I consulted for Barcelona Design.

Simulation-based optimizers provided by Mentor, Cadence and Synopsys are popular to EDA companies because they consume so many SPICE licenses. EDA tool users will be more attracted to the Magma approach because it doesn’t require a compute farm of SPICE licenses.

Before you can optimize your transistor-level design you still need to verify that your Matlab model matches SPICE. The real question is, “How much time does this verification take compared to the benefits of equation-based optimization?”

Finally the Titan Analog Virtual Prototype (AVP) allows you to pre-annotate physical effects during optimization, because at 28nm and 32nm, 40nm the physical effects impact performance greatly, 25% typical. You enter in constraints like: symmetry, matching, proximity, etc.

Summary

Magma has assembled some impressive technology for analog and mixed-signal designers, now let’s see how well the marketplace adopts them.