On Tuesday I met with Richard Shi, Ph.D.,Chairman and CTO of Orora Design Technologies.

This company offered the 1st – optimizer and analog synthesis tool.

They showed me three tools for use by analog design engineers.

Arana – Behavioral model generator (dial in the percentage accuracy needed)

– Bottom up generator (RTL extractor, algebraic reduction)

– Top down generator (like Excel spreadsheet input, create Verilog A netlist, template matching), user defined template matching

– Validation environment (help automate test bench creation)

– Creates Verilog A, Verilog AMS, Verilog models

– Inputs: Netlist or Cadence db, OA

– Optionally optimize your model

– Ask for inputs, outputs (digital or analog)

Arche – Arana input (Beta)

– Creates data sheet verification report

– Re-use testbenches

– Read waveforms and check against spec

– Verify electrical rules

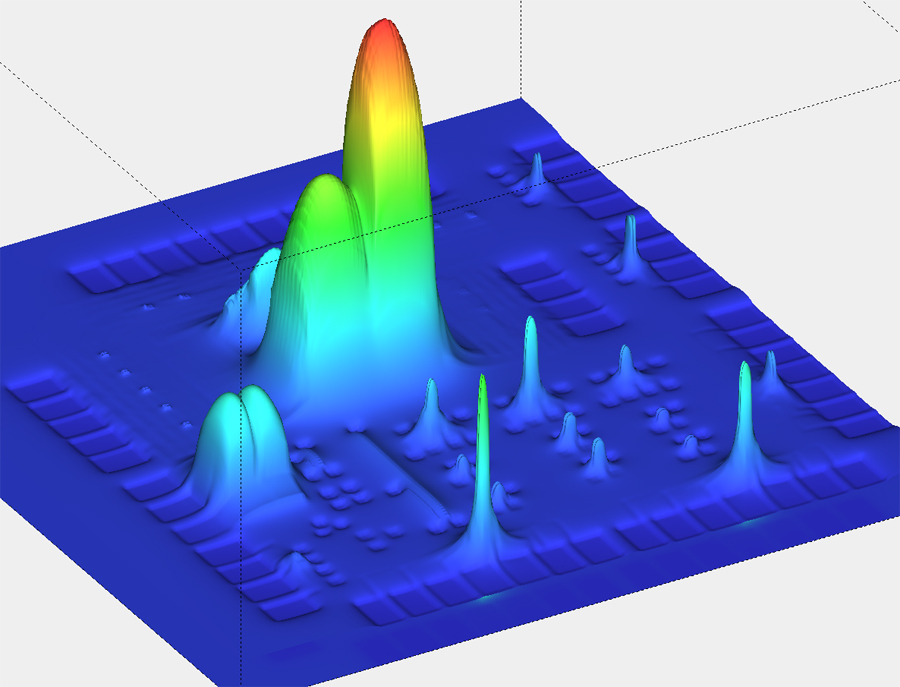

Arsyn – Used for five years, circuit synthesis

– Optimization, creates an optimized circuit design

– Automated design and re-use platform

– Example: DARPA did a ADC, DAC, 600 transistors (5X faster design time, doubled the yield)

– Pricing not disclosed

Arphy – next year tool

– Layout synthesis

Partner Programs – Cadence, Mentor, Synopsys

Mission – automate analog and ams design

Customers – 20 now

Demo – invoke arana from virtuosos GUI (also own gui)

– Model methods (bottom up, structural, functional, template, algebra)

– PLL example with several blocks

– Define which blocks are bottom up

– How to validate each model?

– User provides: pin name, pin direction, discipline (electrical or logic), function (V, I, Vdd, Vss, large, small signal)

– Also generate the analog test bench to simulate my models

– User defines how many parameters to use, how many PVT corners to use

– Validation manager: original stimulus from CDN, run spice on netlist versus

– Which simulators? Any tool (Spectre, Ultrasim, HSPICE, Nanosim)

– Output comparisons of spice versus Verilog A, show % differences.

You can also review our Analog and RF

optimization tools

http://www.ago-inc.com