I talked with Nicholas Williams of Tanner EDA by phone yesterday to learn more about a new product called HiPer DevGen. Their first two analog IC generators are for:

- Differential pairs

- Current mirrors

Q: Why aren’t you following what the IPDK route?

A: We’re focusing on analog IC layout for nodes at 90nm and above to start with. Most of IPDK is focused at 65nm and below nodes with digital designs.

Q: Why would I want to use DevGen?

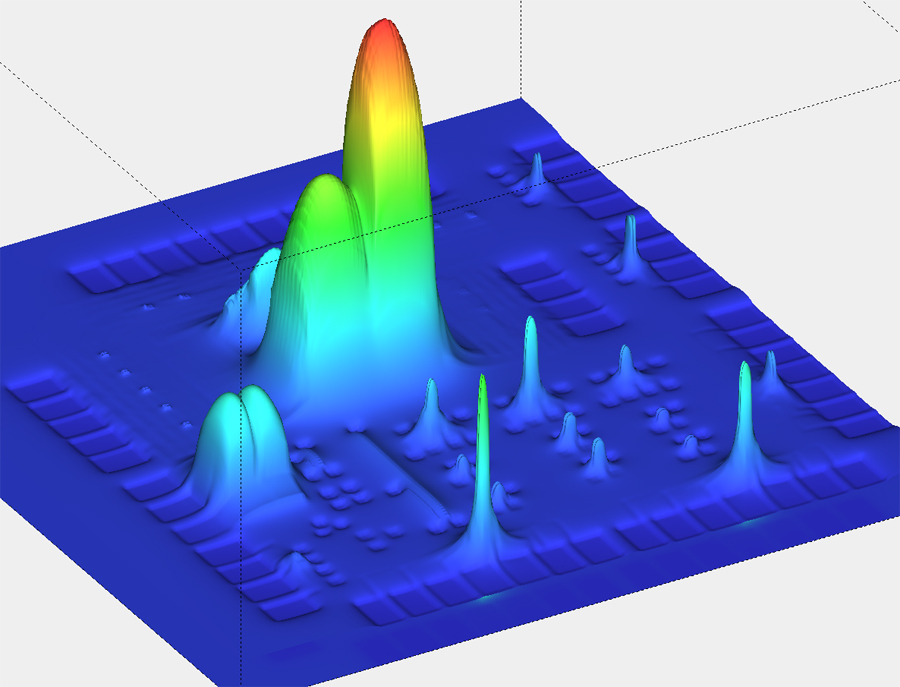

A: These are smart generators that will save you layout time. Our system will analyze your netlist, find the current mirrors and differential pairs, then automatically send them to the generators. The generators consider: mismatch, apply good layout techniques, account for mask mis-alignments, Wpe and stress effects, plus Ld. A layout engineer can quickly change options to adjust the layout aspect ratio and sizes. There’s no code to write, the setup wizards are easy to use and soon you’ll see more foundries supporting Tanner PDKs.

Q: What kind of IC customers does Tanner EDA have?

A: We have some clients designing at the 45nm and 22nm nodes now with our tools. It’s a broad spectrum covering: analog, full-custom, power management and MEMs.

Summary

I wrote my own IC device generators in 1982 while at Intel that created 5% of a full-custom graphics chip. After that I was really hooked on automating everything with IC design and joined my first EDA company in 1986, Silicon Compilers (acquired then down-sized by Mentor Graphics).

Tanner EDA is on the right track here with DevGen and I’d love to see a dozen or more device generators created in the next year.