Last Monday I had a conference call with Nick Williams of Tanner EDA along with Dan Hammond (VP Marketing). In April I blogged about my install and use of their tools.

This 21 year-old, privately held EDA company offers IC and MEMS tools on both Windows and Linux boxes.

They have a research group that actually designs MEMS and imaging chips with Tanner EDA tools. Like Microsoft, time to eat your own dog food. Look at all of the tools they offer:

New in the past year – SDL Router. Multi-layer area router, good for block level routing and top-level assembly. Show fly-lines, move things around.

Analog routing – manual routing on most sensitive nets. Interactive DRC will enforce rules while routing so I can see any edges that are in violation. Stop when I get to the closest spacing.

Auto route – used for non-sensitive nets.

Device Generator – using own generator called Tcells, which are C based. Create generators without writing code, using wizards. Processes are 90nm and older, typically. Tanner distributes these generators. A few foundries will verify these and distribute these generators. These are in competition with Ciranova Pycells, Cadence Pcells, Springsoft MCells, Mentor device generators, etc.

Q: What about iPDK?

A: Plan to add it in the future if demand is seen. Older processes won’t use iPDK.

Assura Support – Released a hierarchical DRC tool, had Calibre native support, now Cadence supported (no translation). Dracula supported before. Direct reading. 40nm and older using HyperVerify.

iDRC, iLVS – to be supported when standardized.

Why choose Tanner?

Fast to learn, Microsoft ui, within one week you are efficient with the tools, not months.

Lower costs. No CAD manager needed. Easy to license, no geography restrictions (mostly perpetual licenses)

Work with de-facto standards – EDIF versions.

L-Edit and S-Edit with Calibre (DRC LVS) – Calibre RVE has a protocol, Tanner made EVI to work with RVE, cross-probe DRC results in Tanner, interfaces with Calibre interactive. Extra integration cost. Also using integration: Cadence, Synopsys, Springsoft?

Foundry support – see recent press releases, some PDK support (X Fab, MHS, L Foundry, AMS, UMC)

Linux support is – Red Hat v4 v5, others unofficial

EVI is also new this year and lets you see Calibre RVE results in Ledit and Sedit tools.

64 bit on Windows – more memory space for larger designs, 64 bit vista is 25% faster than XP. 60% of Windows users have Vista now, 40% still on XP.

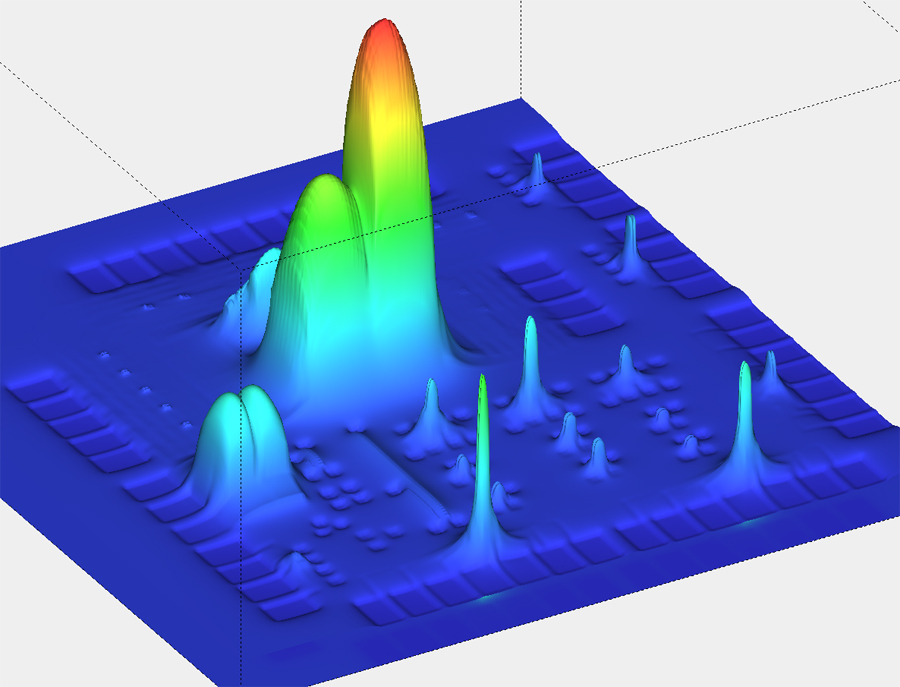

HiPer PX – Parasitic Extraction (2D or 3D extraction using Boundary Element approach) with devices, 3D for use on smaller blocks or a handful of traces on full-chip, 64 bit is coming soon. Can choose between flat or hierarchical extract, tradeoff run time and accuracy. Clock would be 3D extract, or memory bit lines, or diff pair. Has RC netlist reduction built-in, model order reduction based on frequency.

HiPer PX – not using multi-core at all, plan to add compute farm.

DRC, SPICE – use multi-thread and multi-core. All the compute intensive problems in EDA must exploit the multi-core processors that we use each day.

T-SPICE – supports Verilog A syntax. At least it’s a start for the transistor guys that want to learn a little about behavioral modeling to speed up their run times by using abstraction.

MEMS users of Tanner tools include – Proteus Biomedical in WSJ, Beijing Olympics (MEMSIC – waving messages wand) . IC and MEMS together.

Summary

This niche company has built up a working set of tools for analog and mixed-signal IC designs plus MEMS. They have integrated into the major IC EDA competitor flows without adopting Open Access (OA) or IPL (Interoperable PDK Libraries). Finally, they are well-positioned for customers who are looking for a price bargain. They even know how to tweet, @TannerEDA although you cannot find their Twitter address on their home page.