With PowerTrim the idea is to look at your design after placement and routing, find all the paths that still have margin and then selectively upsize the channel lengths to reduce power consumption while maintaining timing specs. Users benefit as these updated cells have reduced leakage because of the CD biasing. In one example I saw a 42% reduction in leakage current while only increasing the path delay by 7%.

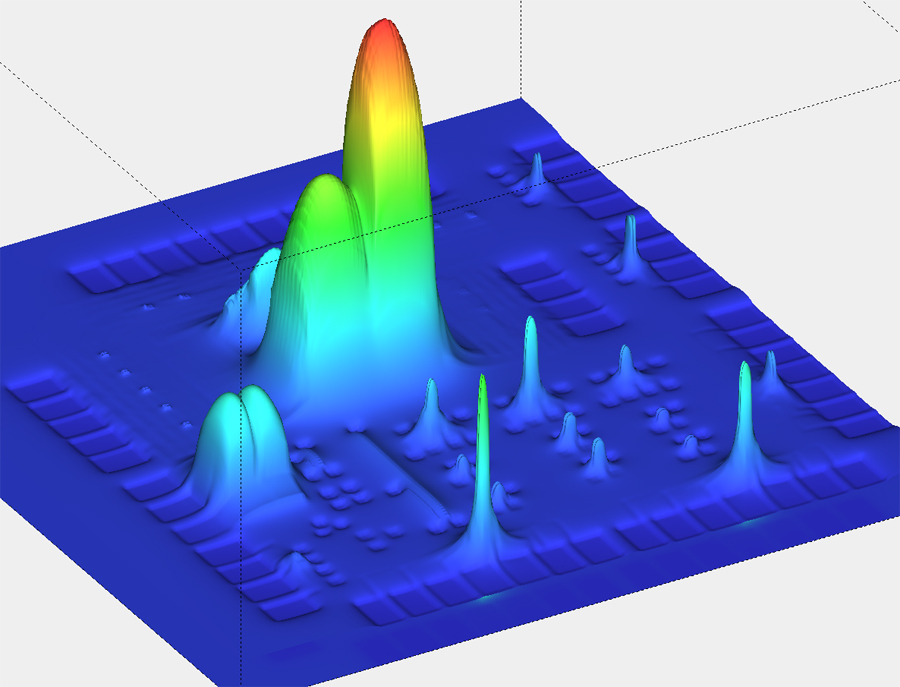

AreaTrim is a way to save up to 20% in layout area by using the new 1D libraries. These new libraries orient all poly gates in one direction, and all metal on the same layer are also oriented in the same direction. From a DFM viewpoint these cells simply print better and therefore yield better.

Client names are soon to be released and the Tela business model is royalty based.

This pragmatic approach at optimizing the 1D cell-level layout to minimize DFM side-effects looks very promising and effective. I would expect that other foundries and even IDMs will follow by copying the success that TSMC and Tela are seeing.