-

Automated Verification for Cache Coherent RISC-V SoCs

RISC-V SoC design complexity continues to increase and create new verification challenges. Private caches, shared caches, and shared main memory create potential caches/memory coherency problems that require modern, automated verification approaches. In this webinar, we’ll demonstrate how Perspec System Verifier, with the pre-defined System Traffic Library (STL), provides an out-of-the-box verification plan and test suite… Automated Verification for Cache Coherent RISC-V SoCs

-

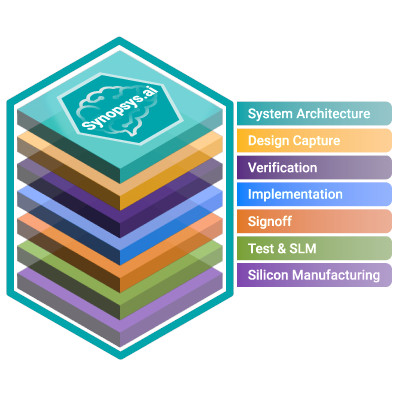

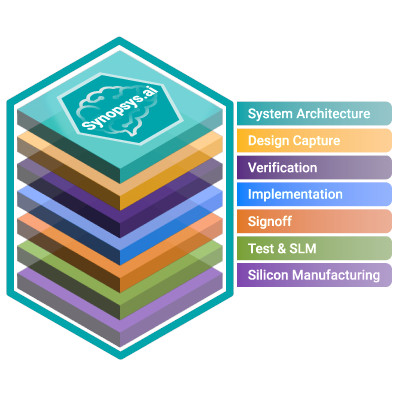

Achieve Optimal PPA Targets Using AI-Driven Technology

Complexity brought on by advanced process nodes have opened the door to challenges in achieving optimal power, performance, and area (PPA). Manual methods are no longer viable given shrinking market windows. The need to drive for better results faster is increasing, and traditional methods cannot keep pace often taking months of tuning using 100s of… Achieve Optimal PPA Targets Using AI-Driven Technology

-

3D-IC Foundry Frameworks

Join us on July 20th; Ansys R&D members will discuss an overview of the 3D-IC technology development frameworks offered by TSMC, Samsung, and Intel and how Ansys simulation tools and workflows fit into those frameworks. About this Webinar Semiconductor applications such as Mobile (5G), Automotive, and Datacenter (HPC, AI) demand better scaling, performance, and lower… 3D-IC Foundry Frameworks

-

Achieve First-pass Silicon Leveraging SDC Verification Early with No Noise

As today’s designs are getting more complex, design constraints complexity also increases multifold. While ensuring design correctness typically gets a lot of attention including code review, functional verification, implementation, etc., correctness of constraints requires the same level of attention. Quality of implementation and timing analysis is highly dependent on quality of constraints. For achieving first-past… Achieve First-pass Silicon Leveraging SDC Verification Early with No Noise

-

International Test Conference – India, 2023

Radisson Blu Outer King Road, Bengaluru, IndiaInternational Test Conference is the world’s premier venue dedicated to the electronic test of devices, boards and systems-covering the complete cycle from design verification, design-for-test, design-for-manufacturing, silicon debug, manufacturing test, system test, diagnosis, reliability and failure analysis, and back to process and design improvement. At ITC India, design, test, and yield professionals can confront challenges… International Test Conference – India, 2023

-

ITC India 2023

Hotel Radisson Blu Marathalli ORR, Bengaluru, IndiaKeynote speakers Fadi Maamari VP of Engineering at Synopsys Sule Ozev Arizona State University About Us International Test Conference is the world’s premier venue dedicated to the electronic test of devices, boards and systems-covering the complete cycle from design verification, design-for-test, design-for-manufacturing, silicon debug, manufacturing test, system test, diagnosis, reliability and failure analysis, and back… ITC India 2023

-

Solution for 3D-IC Interposer Signal Integrity

Our upcoming CadenceTECHTALK: Solution for 3D-IC Interposer Signal Integrity is designed to teach engineers to translate a GDSII stream format (GDSII) file and partition it into simulation blocks for the Clarity 3D field solver. First, you will learn to use GDS-supporting files to simplify GDS to SPD translation and reuse those files to make the… Solution for 3D-IC Interposer Signal Integrity

-

Solution for 3D-IC Interposer Signal Integrity

3D-IC design requires early analysis of thermal properties, power delivery, and signal integrity. This webinar will work through the process of simulating heterogeneously integrated chiplets. Learn about the integrated workflow that begins with silicon design data being accurately modeled with 3D FEM extraction. The Cadence Clarity 3D Solver has the unique ability to efficiently import… Solution for 3D-IC Interposer Signal Integrity

-

A Novel Approach to Implementing Logical ECOs with Synopsys Formality ECO on High Performance RISC-V Cores

RTL engineering change order (ECO) is vital to ensuring proper functionality of integrated circuits (ICs). Retiming and auto ungrouping optimize RTL implementation and enhance PPA. However, aggressive optimizations in CPU RTL designs present challenges due to increased design complexity and potential mapping issues. Synopsys Formality ECO offers an efficient and accurate solution for RTL ECO… A Novel Approach to Implementing Logical ECOs with Synopsys Formality ECO on High Performance RISC-V Cores

-

EMC+SIPI 2023

DeVos Place 303 Monroe Ave NW, Grand Rapids, MI, United StatesEMC+SIPI 2023 leads the industry in providing state-of-the-art education on EMC and Signal Integrity and Power Integrity techniques. Don't miss out on this valuable opportunity to learn from and network with industry leaders and peers.

-

Accelerate Coverage Closure with Synopsys VSO.ai

70% of engineering time is spent verifying a design but it is largely a manual effort. As the industry faces ongoing engineering shortages companies are forced to make their engineering teams 10 times more productive at finding and isolating bugs per day. Increasing design complexities are also driving up the compute resources needed to verify… Accelerate Coverage Closure with Synopsys VSO.ai

-

An Introduction to Correct-by-Construction Golden Specification-based IP/SoC Development

This webinar explores front-end automation advances that encompass an innovative register information management system to capture hardware functionality and addressable register map in a single "executable" specification. Appropriate Audience: ● Architects/RTL Designers ● Verification Engineers ● Pre-Silicon Validation Teams ● Post-Silicon Lab Bring-up Team Members ● Technical Writers ● Firmware Engineers ● Embedded Programmers Learn… An Introduction to Correct-by-Construction Golden Specification-based IP/SoC Development

12 events found.