-

Has the Time for Analog Automation Finally Come?

The semiconductor industry is experiencing explosive growth, driven by emerging applications such as AI, 5G, IoT and automotive. To keep pace, design teams have deployed sophisticated CAD tools that can implement digital designs comprising billions of transistors. However, while digital design has been extensively automated, analog continues to require handcrafting by experts. In this talk… Has the Time for Analog Automation Finally Come?

-

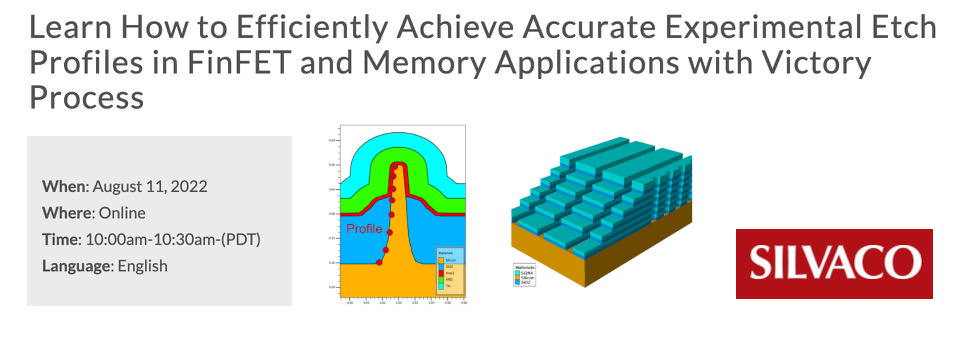

Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

When employing process simulation to generate a complex device structure, TCAD engineers often face the task of reproducing the exact etch profile that has been observed in semiconductor fabrication. Silvaco Victory Process offers several geometric models to efficiently achieve etch geometries that accurately match microscopy images (e.g., transmission electron microscopy). In this webinar, we present… Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

-

CAD for Assurance: Panel 5: Hardware Assurance vs. AI: Friend or Foe?

Moderators: Ankur Srivastava (U. of Maryland) and Swarup Bhunia (U. of Florida) Panelists: - Mike Borza, Synopsys - Brian Night, Microsoft - Pompei Len Orlando, Air Force Research Lab (AFRL) - Antonio de la Serna, Siemens - Samuel M Weber, Office of Naval Research (ONR) 90-min panel Assurance of electronic hardware against diverse security and… CAD for Assurance: Panel 5: Hardware Assurance vs. AI: Friend or Foe?

-

Fast and Accurate Functional ECOs with Synopsys Formality ECO

To achieve maximal quality of results (QoR) in synthesis, it requires leveraging retiming, multibit banking, and advanced datapath optimizations, which are part of the Synopsys Fusion Compiler™ implementation solution. However, during the late-stage functional ECO (engineering change order) phase, the automated ECO tool needs to be sophisticated enough to generate optimal patches in the presence… Fast and Accurate Functional ECOs with Synopsys Formality ECO

-

Sustainability for Semiconductors

Don’t miss your chance to join this important conversation with industry leaders that are making an impact on the reduction of the semiconductor carbon footprint. Donna Yasay Senior Leader, Solutions Architecture at Amazon Web Services (AWS) Donna Yasay leads a solution architecture team for the Bay Area semiconductor segment at Amazon Web Services (AWS). Her team… Sustainability for Semiconductors

-

FPGAs for AI and AI for FPGAs

Artificial Intelligence (especially Deep Learning) is rapidly becoming the cornerstone of numerous applications, creating an ever-increasing demand for efficient Deep Learning (DL) processing. FPGAs provide massive parallelism, while being flexible and easily configurable, and also fast and power efficient. These unique properties make them appealing for DL acceleration in both data center and edge use… FPGAs for AI and AI for FPGAs

-

Design and Verify State-of-the-Art RFICs using Synopsys / Ansys Custom Design Flow

Wireless communication is at the heart of the technological revolution of the past few decades and RF circuits are what enable wireless systems to communicate with each other. The design and characterization of RF circuits is a complex process that requires the designer to account for a variety of challenges. In addition to the challenges… Design and Verify State-of-the-Art RFICs using Synopsys / Ansys Custom Design Flow

-

A Key principle to successful tape-outs for Cadence Virtuoso users 10am PDT

As working remotely and virtually has become the new norm, collaboration and coordination between colleagues has its challenges and its obstacles. If you are using Cadence Virtuoso and working on schematics and layouts we will show you in this webinar methodologies which more and more engineers have adopted in managing the various revisions seamlessly. We… A Key principle to successful tape-outs for Cadence Virtuoso users 10am PDT

-

Centralized Register Design and Verification from a Golden Specification

Learn how to bring the ease of a document editor to your system architects and designers to create an executable specification using IDesignSpec™. This specification fully describes and documents your design and automatically generates all downstream views. IDesignSpec™ enables IP, SoC, and FPGA teams to standardize on your register specification and generate Verilog, VHDL, UVM, C… Centralized Register Design and Verification from a Golden Specification

-

Hot Chips 2022

HC34(2022) (advance program) will take place virtually from Sunday, August 21 - Tuesday, August 23, 2022. All HC33(2021) conference content open to public. Visit https://hc33.hotchips.org. Since it started in 1989, HOT CHIPS has been known as one of the semiconductor industry’s leading conferences on high-performance microprocessors and related integrated circuits. The conference is held once a… Hot Chips 2022

-

SPIE Optics + Photonics 2022

San Diego Convention Center 111 W. Harbor Drive, San Diego, CA, United StatesJoin your peers and heroes in San Diego You will find plenty to like at this important meeting, including over 2,000 presentations and the latest technical results within 48 conference topics. This is the best opportunity to connect face-to-face for discussions about optical engineering and applications, nanotechnology, quantum science, and organic photonics. Escape the everyday… SPIE Optics + Photonics 2022

-

PSI-K Conference

SwissTech Convention Center Lausanne, SwitzerlandThe conference will be the 6th general conference for the worldwide Psi-k community, following very successful events held in San Sebastian (2015), Berlin (2010), and Schwäbisch Gmünd (2005, 2000, 1996). This major conference – the largest worldwide in electronic-structure – brings together the community that is active in the field, as described by the Psi-k… PSI-K Conference

12 events found.