-

-

CadenceTECHTALK: Power and Energy Optimization Using Tensilica IP

Join us as Cadence experts describe common challenges and solutions in creating an efficient and accelerated flow that will meet technical requirements for accurately measuring the power, energy, and system performance while making essential design tradeoffs to meet your aggressive time-to-market schedule. In this CadenceTECHTALK, you will learn how to: Address the challenges of accelerating… CadenceTECHTALK: Power and Energy Optimization Using Tensilica IP

-

Samsung SAFE Forum 2021

Join us for Samsung Foundry’s annual SAFE™ Forum. What will you take away from Samsung Foundry’s ecosystem event? Bump your SoC PPA knowledge with the latest information on: High speed interconnect IPs for HPC and Data Center applications and foundational IPs High bandwidth memory subsystems Key IP trends for automotive and mobile applications Foundational Analog… Samsung SAFE Forum 2021

-

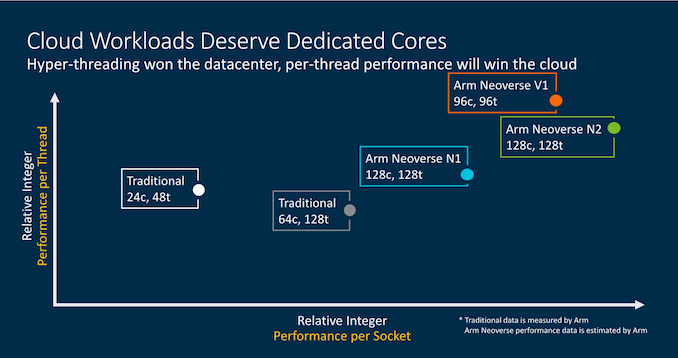

A Scalable Approach to 2X Faster Turnaround Time for Arm Neoverse N2 Core Design Verification

In the latest generation of multiple processor SoCs, designers are adding cache-coherent agents beyond the multi-processor clusters, making it a complex verification challenge. System coherency needs to be maintained at various levels, beginning at the cluster level, and continuing, across the cache coherent interconnect and across chips through chip-to-chip gateways. The coherency protocol across interconnects… A Scalable Approach to 2X Faster Turnaround Time for Arm Neoverse N2 Core Design Verification

-

Accelerate Semiconductor Technology Development and Innovation

Seminar Overview Join our online TCAD Seminar to learn about the application of Synopsys TCAD solutions to accelerate the research, development and optimization of semiconductor technologies. The seminar tracks cover all major semiconductor technologies, from advanced logic and memory to analog, power and optoelectronics. The solutions presented in this seminar are based on the industry-standard… Accelerate Semiconductor Technology Development and Innovation

-

SURGE Virtual Event Taiwan 2021

November 18, 2021 - 13:30PM -17:10PM (Chungyuan Standard Time) Silvaco is pleased to invite you to join its annual SURGE users event, taking place virtually, on Thursday November 18, 2021. SURGE brings the TCAD, EDA, and IP communities together to discuss new technologies, share users’ experiences, and discover innovative techniques for advanced semiconductor design. This… SURGE Virtual Event Taiwan 2021

-

FPGA Conference and Hackathon

We are changing the world through this. So you can! Join the FPGA Hackathon we organize in Kraków to learn more about the technology gaining more and more popularity! Sharing this passion is the reason why we decided to create this Conference and Hackathon. FPGA technology is one of the foundations for the revolutionary projects… FPGA Conference and Hackathon

-

Everything you wanted to know about VHDL configurations

VHDL configurations are a much maligned, much ignored part of the VHDL language. Consequently, many VHDL designers find them quite scary. This webinar seeks to answer the questions you may not have had answered in the past; shedding light on the mystery of VHDL configurations and showing a practical example of how to apply them,… Everything you wanted to know about VHDL configurations

-

-

IP-SoC Conference 21

IP-SoC 2021 will be the 24th edition of the working conference fully dedicated to IP (Silicon Intellectual Property) and IP based electronic systems. The event is the annual opportunity for IP providers and IP consumers to share information about technology trends, innovative IP SoC products, Breaking IP/SoC News, Market evolution and more. The Grenoble event is… IP-SoC Conference 21

-

Optimal circuit sizing strategies for performance, low power, and high yield of analog and full custom IP

There have always been good reasons to port designs to new foundries or processes. These reasons have included reusing IP in new projects, moving an entire design to a smaller node to improve PPA, or second sourcing manufacturing. While there can be many potential business motivations for any of the above, in today’s environment with… Optimal circuit sizing strategies for performance, low power, and high yield of analog and full custom IP

-

How to Sign Off a 10 Billion+ Transistor Design in the Cloud

Advanced semiconductor applications such as artificial intelligence / machine learning (AI/ML) and graphic processing units (GPUs) fully leverage dense, advanced-node technology to push the extreme limits of design size. To signoff such large designs, engineers are increasingly relying on distributed compute methods to accelerate the signoff analysis. Furthermore, given lack of scalability of on-premises compute… How to Sign Off a 10 Billion+ Transistor Design in the Cloud

-

LIVE WEBINAR: How to Simplify the Verification of Bus Interfaces (US)

Abstract: Today’s FPGAs and SoC FPGAs use various types of bus interconnect - such as AXI, APB, AHB, Avalon or Wishbone - for both internal (IP-level) and external communication. A recently added feature to Aldec’s ALINT-PRO allows designers to extract, review and verify the correctness of bus interface connections. In addition, ALINT-PRO is capable of… LIVE WEBINAR: How to Simplify the Verification of Bus Interfaces (US)

-

58th Design Automation Conference

Moscone Center 747 Howard Street, San Francisco, CA, United StatesThe Design Automation Conference (DAC) is the premier event devoted to the design and design automation of electronic systems and circuits. DAC focuses on the latest methodologies and technology advancements in electronic design. The 58th DAC will bring together researchers, designers, practitioners, tool developers, students and vendors.

12 events found.