-

Optimized Chip Design with Main Processors and AI Accelerators

Presented by Paul Karazuba, VP of Marketing, Expedera & John Min, Director of Field Application Engineering, Andes Technology About this talk As AI capability is beginning large-scale deployment into edge devices, many wonder about the decision to use a specialized AI accelerator, rather than simply using the systems main processor. In this first of two… Optimized Chip Design with Main Processors and AI Accelerators

-

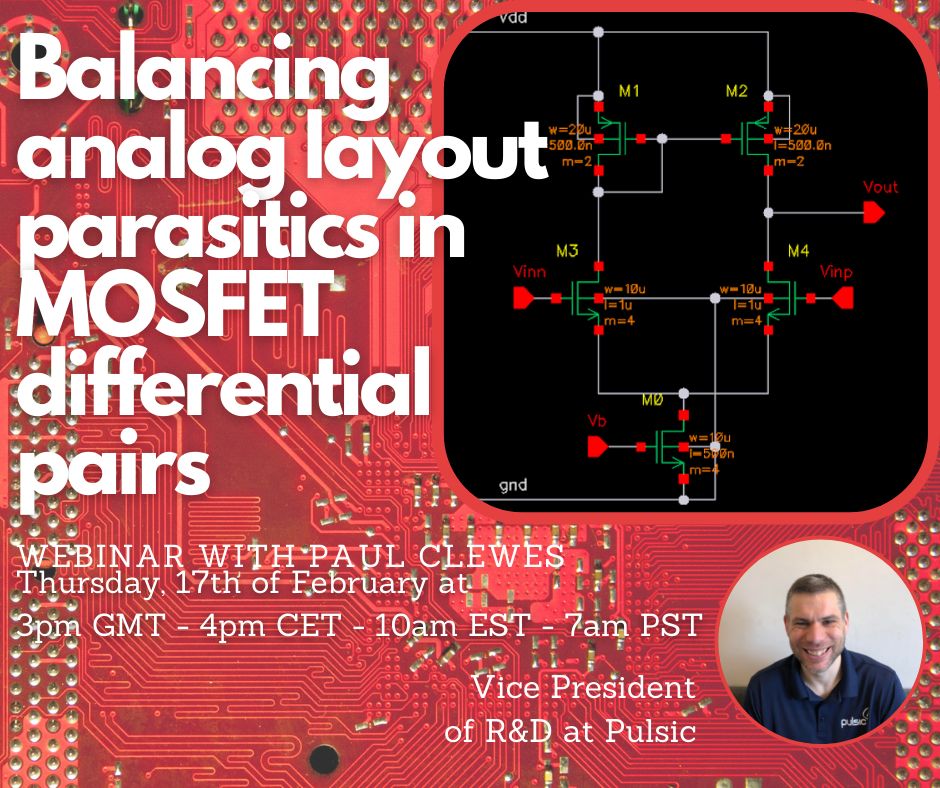

Balancing analog layout parasitics in MOSFET differential pairs

The MOSFET differential pair is a key part of many analog circuits e.g. opamps, comparators, LDOs, etc. A differential pair applies gain to the difference between two signals and has many advantages over single-ended amplifier circuits, e.g. noise reduction and suppression of common-mode signals and DC offset. However, these advantages rely upon precisely matched circuit… Balancing analog layout parasitics in MOSFET differential pairs

-

How to Improve Physical Verification Productivity with SmartDRC/LVS

Physical Verification is the most critical stage of IC design. SmartDRC/LVS is a new physical verification tool for analog, digital and mixed-signal ICs including design rule checks (DRC), layout connectivity extraction and layout vs schematic (LVS) comparisons. Its unique multi-CPU architecture delivers high performance and capacity, accurate processing of complex shapes, and exceptional user productivity… How to Improve Physical Verification Productivity with SmartDRC/LVS

-

Open-Source FPGA: Towards Fully Automated FPGA Tapeout Flows

In this webinar, we will present the open-source FPGA tools which automate the tapeout flow for custom FPGA fabrics. We will cover the key steps involved in the process when using the tools, including netlist generation, design verification and performance prediction. We will also introduce the latest features in open-source FPGA and explain how they… Open-Source FPGA: Towards Fully Automated FPGA Tapeout Flows

-

Mixed-Signal SoC Verification Simplified with Xcelium Simulator

Analog and mixed-signal verification has always been a challenge for design and verification engineers. It has become tedious with the increasing complexity of SoC designs. Because the analog behavior of key design blocks cannot be simulated effectively using traditional verification methodologies, new methodologies and solutions like real number modeling (RNM) for analog functional blocks are… Mixed-Signal SoC Verification Simplified with Xcelium Simulator

-

SemIsrael Tech Webinar

SemIsrael Expo is the premier professional semiconductor event in Israel. The event brings together hundreds of Israeli semiconductor professionals from all fields and aspects of the semiconductor industry. The Expo will host some 750 semiconductor professionals from all the Israeli semiconductor community; local fabless & startups, local R&D offices of multinationals and IDMs, foundries, design… SemIsrael Tech Webinar

-

Connect Your System Architecture Design and Implementation

Join Cadence Training and Senior Application Engineer Dave Palumbo for this free technical Training Webinar. The disconnect between system architecture design and implementation makes creating a system that meets cost, performance, and form factor requirements challenging. Hardware designers need tools that help them engineer systems to meet the goals of their end products within the… Connect Your System Architecture Design and Implementation

-

The Role of PUFs in a Trusted Supply Chain

Trusted supply chain provenance and traceability is becoming increasingly important for the quality, reliability, and security of electronic products. It can help reduce costs for tracking and fixing field issues, minimize liability risks and enable higher value in connected IoT applications. In addition, there are significant efficiencies and cost reductions that could be enabled in… The Role of PUFs in a Trusted Supply Chain

-

CadenceTECHTALK: Efficient Multi-Chiplet Design with Integrity 3D-IC Unified Platform

Multi-chiplet design and packaging introduces extra design and analysis requirements like system planning, bump alignment, TSV and micro-bump insertion and extraction, electrothermal analysis, cross-die STA, and inter-die physical verification, which must be considered early during planning and implementation. The new Cadence® Integrity™ 3D-IC platform provides innovative technology that proactively looks ahead through integrated planning, implementation,… CadenceTECHTALK: Efficient Multi-Chiplet Design with Integrity 3D-IC Unified Platform

-

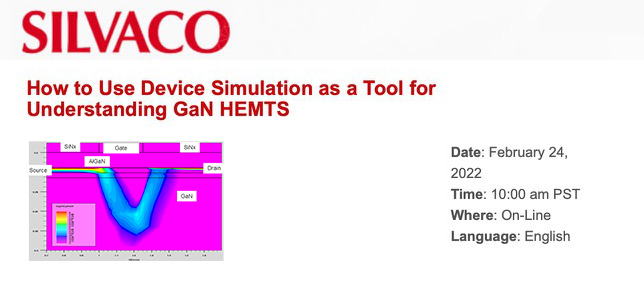

How to Use Device Simulation as a Tool for Understanding GaN HEMTS

Gallium Nitride based devices are highly attractive for both RF and power switching applications due to a combination of outstanding materials properties. However, although the basic principles are well understood and can now be accurately reproduced in device simulators, there are many important aspects that are still poorly understood and the subject of continuing active… How to Use Device Simulation as a Tool for Understanding GaN HEMTS

-

Automating UVM flow using Riviera-PRO’s UVM Generator

UVM is a versatile verification methodology that enables users to run advanced verification flows for large scale FPGAs and SoC FPGAs. However, because of its advanced nature, writing UVM from scratch can be a complex and tedious task. Riviera-PRO’s new UVM Generator feature alleviates some of the complexity by automatically creating the UVM testbench for… Automating UVM flow using Riviera-PRO’s UVM Generator

-

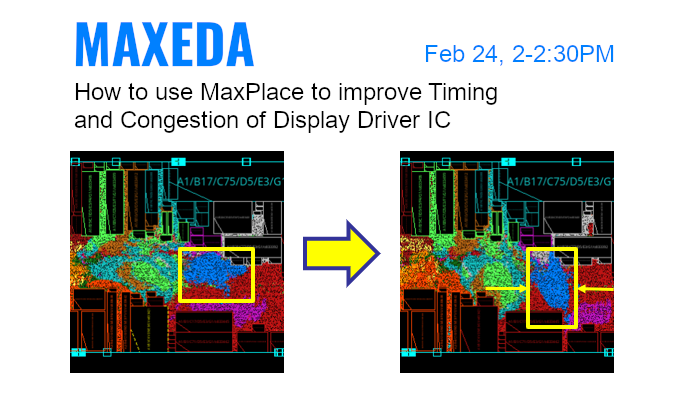

How to use MaxPlace to improve Timing and Congestion of Display Driver IC

Agenda: •Maxeda Highlight •Product Overview •Display Driver IC Challenges for Congestion/Timing •MaxPlace Solutions for Display Driver IC •Our next step - ML •Q&A

12 events found.