-

-

Complete STA Workshop with OpenSTA

In this program you will get access to: 10 hours of training videos access for the lifetime Access to reading material with sample codes for the lifetime 1.5hr Q/A sessions every day of the workshop Telegram Cohort Group for the duration of the workshop to ask questions doubts Assignments and labs to with instructor help… Complete STA Workshop with OpenSTA

-

AI-Driven Verification: Saving Time with Verdi Regression Debug Automation

Analyzing the thousands of failures from daily regression runs is a manual, tedious, and error-prone process. The process can significantly impact quality-of-results, time-to-results and cost-of-results. The Synopsys Verdi® Regression Debug Automation (RDA) is an artificial intelligence (AI) driven verification technology for automating the process of finding the root causes of failures in the design under… AI-Driven Verification: Saving Time with Verdi Regression Debug Automation

-

-

EMC+SIPI 2022

The Spokane Convention Center 334 W Spokane Falls Blvd, Spokane, WA, United StatesEMC+SIPI 2022 leads the industry in providing state-of-the-art education on EMC and Signal Integrity and Power Integrity techniques. On behalf of the IEEE EMC Society, I invite you to join us over August 1-5, 2022 in beautiful Spokane, Washington for our annual symposium. After two years of virtual symposia, we are looking forward to meeting… EMC+SIPI 2022

-

Flash Memory Summit

Santa Clara Convention Center 5001 Great America Parkway, Santa Clara, CA, United StatesProgram It is ideal for consumer applications such as cellphones, digital cameras, and music players, and is also useful in computers, communications systems, and military/defense applications. It can replace hard disks for storage in applications where its higher cost is balanced by its smaller size, greater ruggedness, and lower power consumption. The summit consists of:… Flash Memory Summit

-

Advanced Physical Design using OpenLANE/Sky130

Physical Design or PnR (Place and Route) is the core of any IC design cycle. From a RTL netlist to final tape-out, each phase of PnR brings it’s own challenges and surprises. “What are these challenges?” “What is the process?” “Can I build a chip of my own?”- If you have these questions and if… Advanced Physical Design using OpenLANE/Sky130

-

A Smart and Automatic Assembly and Connections for SoCs

Learn how to automatically assemble and connect IPs from many different sources at your SoC level using SoC Enterprise™. This includes automatic generation of components such as aggregators, bridges, channels, bus fabrics, muxes, etc. wherever needed.

-

2022 R2: What’s New in Ansys Signal & Power Integrity

About this Event The 2022 R2 Ansys Signal and Power Integrity release introduces significant simulation improvements for electronic printed circuit boards, IC packages, and interposers. Ansys SIwave delivers new features, including a new blending algorithm for AC-DC transition, enhancements for DDR Wizard, which now supports IBIS AMI models, RLCG matrix reduction operations in CPA, and… 2022 R2: What’s New in Ansys Signal & Power Integrity

-

Has the Time for Analog Automation Finally Come?

The semiconductor industry is experiencing explosive growth, driven by emerging applications such as AI, 5G, IoT and automotive. To keep pace, design teams have deployed sophisticated CAD tools that can implement digital designs comprising billions of transistors. However, while digital design has been extensively automated, analog continues to require handcrafting by experts. In this talk… Has the Time for Analog Automation Finally Come?

-

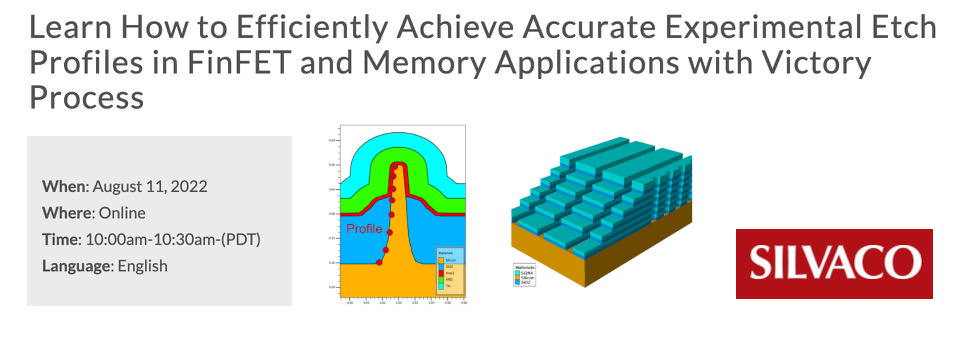

Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

When employing process simulation to generate a complex device structure, TCAD engineers often face the task of reproducing the exact etch profile that has been observed in semiconductor fabrication. Silvaco Victory Process offers several geometric models to efficiently achieve etch geometries that accurately match microscopy images (e.g., transmission electron microscopy). In this webinar, we present… Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

-

CAD for Assurance: Panel 5: Hardware Assurance vs. AI: Friend or Foe?

Moderators: Ankur Srivastava (U. of Maryland) and Swarup Bhunia (U. of Florida) Panelists: - Mike Borza, Synopsys - Brian Night, Microsoft - Pompei Len Orlando, Air Force Research Lab (AFRL) - Antonio de la Serna, Siemens - Samuel M Weber, Office of Naval Research (ONR) 90-min panel Assurance of electronic hardware against diverse security and… CAD for Assurance: Panel 5: Hardware Assurance vs. AI: Friend or Foe?

-

Fast and Accurate Functional ECOs with Synopsys Formality ECO

To achieve maximal quality of results (QoR) in synthesis, it requires leveraging retiming, multibit banking, and advanced datapath optimizations, which are part of the Synopsys Fusion Compiler™ implementation solution. However, during the late-stage functional ECO (engineering change order) phase, the automated ECO tool needs to be sophisticated enough to generate optimal patches in the presence… Fast and Accurate Functional ECOs with Synopsys Formality ECO

-

Sustainability for Semiconductors

Don’t miss your chance to join this important conversation with industry leaders that are making an impact on the reduction of the semiconductor carbon footprint. Donna Yasay Senior Leader, Solutions Architecture at Amazon Web Services (AWS) Donna Yasay leads a solution architecture team for the Bay Area semiconductor segment at Amazon Web Services (AWS). Her team… Sustainability for Semiconductors

12 events found.