Aldec

Events

-

-

FPGA Conference and Hackathon

We are changing the world through this. So you can! Join the FPGA Hackathon we organize in Kraków to learn more about the technology gaining more and more popularity! Sharing this passion is the reason why we decided to create this Conference and Hackathon. FPGA technology is one of the foundations for the revolutionary projects…

-

-

LIVE WEBINAR: How to Simplify the Verification of Bus Interfaces (US)

Abstract: Today’s FPGAs and SoC FPGAs use various types of bus interconnect - such as AXI, APB, AHB, Avalon or Wishbone - for both internal (IP-level) and external communication. A recently added feature to Aldec’s ALINT-PRO allows designers to extract, review and verify the correctness of bus interface connections. In addition, ALINT-PRO is capable of…

-

-

Increase your productivity with Continuous Integration flows

Abstract: In a team environment, verification engineers push code changes every day, and sometimes several times a day, to a shared repository. Each change has the potential to introduce new bugs into the design. Accordingly, when many changes are being made, it is difficult to pinpoint which one introduced new bugs, and much time can…

-

-

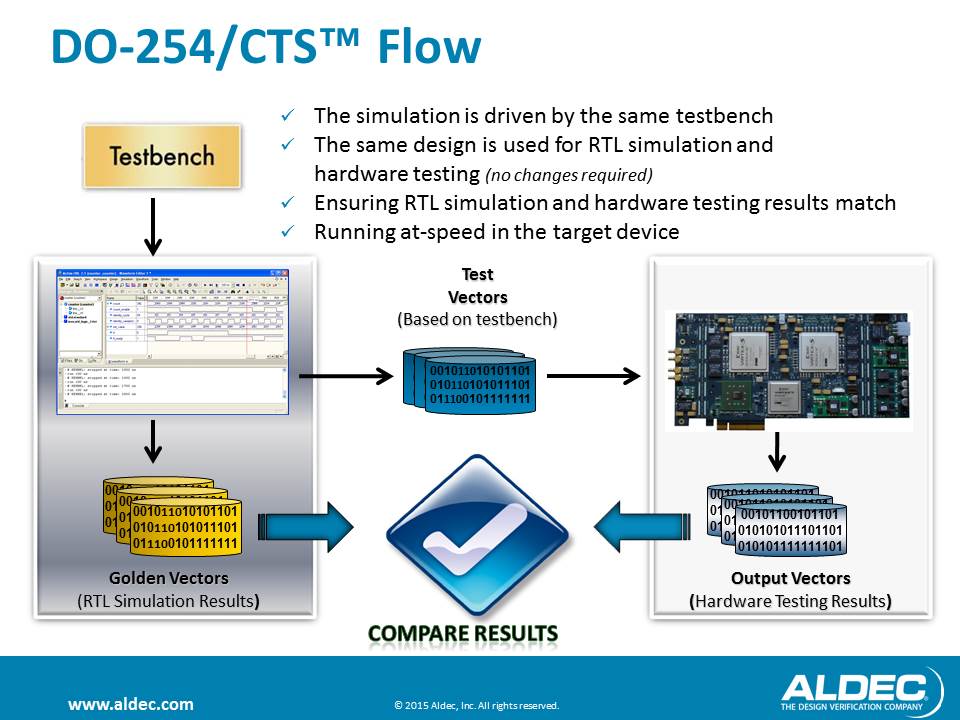

Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance (US)

PCIe-based FPGA designs are becoming popular within avionics systems. However, the verification of such designs for DO-254 compliance with design assurance level (DAL) A or B is problematic. FPGA designs that use asynchronous clocks with multiple high-speed serial interfaces such as PCIe produce non-deterministic results during physical tests. Simulation results are optimized because they are…

-

Automating UVM flow using Riviera-PRO’s UVM Generator

UVM is a versatile verification methodology that enables users to run advanced verification flows for large scale FPGAs and SoC FPGAs. However, because of its advanced nature, writing UVM from scratch can be a complex and tedious task. Riviera-PRO’s new UVM Generator feature alleviates some of the complexity by automatically creating the UVM testbench for…

-

FPGA 22

The ACM/SIGDA International Symposium on Field-Programmable Gate Arrays is a premier conference for presentation of advances in FPGA technology. Accepted papers will be published in the conference proceedings and available in the ACM Digital Library. Virtual Conference February 27 – March 1, 2022 Registration now open at: www.isfpga.org/registration Statement from the General Chair: We have made…

-

-

Using SVA for Requirements-Based Verification of Safety-Critical FPGA Designs

Requirements-based verification (RBV) is a popular verification process for FPGA designs used in safety-critical systems. The effectiveness of RBV is limited by the quality and precision of the requirements. Verification techniques such as constrained random verification with assertion-based verification (ABV) can be used to help identify ambiguous or incomplete requirements early in the design and…

-

-

Running CDC Analysis with Xilinx Parameterized Macros

Designing FPGAs that use a single clock domain is a luxury that very few of us have. Modern FPGA designs must cope with multiple clocks running at different frequencies, very often asynchronous to each other, and still be expected to work reliably. Xilinx Parameterized Macros (XPM) can be used to implement CDC, FIFO and BRAM…

-

Webinar: FPGA Design Architecture Optimization

The FPGA design architecture is the single most important and primary factor in achieving development efficiency, quality and reliability. The difference between a good and a bad design architecture can be about 50% of the workload and a high degree of detected and undetected bugs. Most design architectures can be improved and optimized to increase…

-

-

FPGA Verification Architecture Optimization with UVVM

Presenter: Espen Tallaksen, CEO of EmLogic Thursday, May 5, 2022 Abstract: For most FPGA projects, over 50% of the overall project time is spent on verification. This time can be significantly reduced if the verification architecture is well-structured and developed with a focus on reuse. In this webinar, we will show you how to make…

-

FPGA Design/Verification: Randomization

Randomization is very important for modern verification. Still, very few designers apply randomization sufficiently in their testbenches. This means they are missing out on a very important method for finding potential bugs in their design, and as a result their products have significantly more undetected bugs. Randomization can be used in many ways, but it…

-

FPGA Design/Verification: Code, Functional and Specification Coverage

Functional coverage is often mentioned together with constrained-random verification, and this is a great combination. However, functional coverage is also very useful even if you have no randomization at all. This is a great method for ensuring that you are in fact checking the right things in your testbench. Unfortunately, not many designers are applying…