Mirabilis

Events

-

-

Evaluating UCIe based multi-die architectures to meet timing and power constraints

Multi-die architectures have evolved from proprietary to industry standard UCIe. UCIe can accommodate the bulk of designs today from 8 Gbps per pin to 32 Gbps per pin for high-bandwidth applications from networking to Hyperscale data centers. To help your UCIe adoption journey, we present VisualSim Architect and the associated UCIe/PCIe6.0 IPs to explore and…

-

-

Accelerated development in Automotive E/E Systems using VisualSim Architect

We have put together a webinar on November 10th titled: Accelerated development in Automotive E/E Systems using VisualSim Architect . We will provide an introduction to the available features and utilities in VisualSim architect for Automotive Networking, Hardware ECU and Software design exploration. We will present use cases in ADAS, braking, FuSa, AI accelerator enhanced…

-

-

Automotive Ethernet Congress

Hilton Munich Airport Terminalstraße Mitte 20, 85356 München-Flughafen, Munich, GermanyThe ninth Automotive Ethernet Congress to be held on March 21 - 23, 2023 at the Hilton Munich Airport will look to address the following questions: Does the selected transmission technology support the transformation of the E/E architecture from hardware-based to software-centric? Does it offer the necessary flexibility and self-learning capability to be able to continuously…

-

Mapping SysML to hardware architecture

In this webinar, we will show how the SysML behavior models of a RADAR application can be mapped to a architecture model to measure the latency, throughput, power consumption, scheduling quality and response to bottleneck conditions. The application can be quickly mapped onto different architectures to meet the project requirements. This will enable better tuning…

-

-

Choosing the best modeling abstraction for your analysis

This webinar cover the modeling abstraction in the design of electronics, semiconductors and software. This webinar will definitely improve your modeling skills! --Is the abstraction right for your application and design goal? --How do you accelerate the simulation using abstraction? --Can you change the model of computation using abstraction to simplify the modeling effort? During…

-

-

DENSO discusses Verification of network relay performance using VisualSim

Want to learn how Tier One suppliers are using network modeling and simulation in the design and optimization of network topology and gateway architecture. Then attend this Webinar by DENSO. Efficient in-vehicle network development through simulation combining network and ECU hardware and software elements Time Zone: Japan - 3:00 PM (In Japanese) Asia - 3:00…

-

-

DVCon India 2023

Radisson Blu Outer King Road, Bengaluru, IndiaOn behalf of the DVCon India 2023 steering committee, it is my pleasure to welcome you all to the 8th edition of the Design and Verification Conference in India planned from 13- 14th September 2023 as an In-Person conference. We want to carry forward the momentum, excitement and the enthusiasm witnessed during last year’s edition into…

-

-

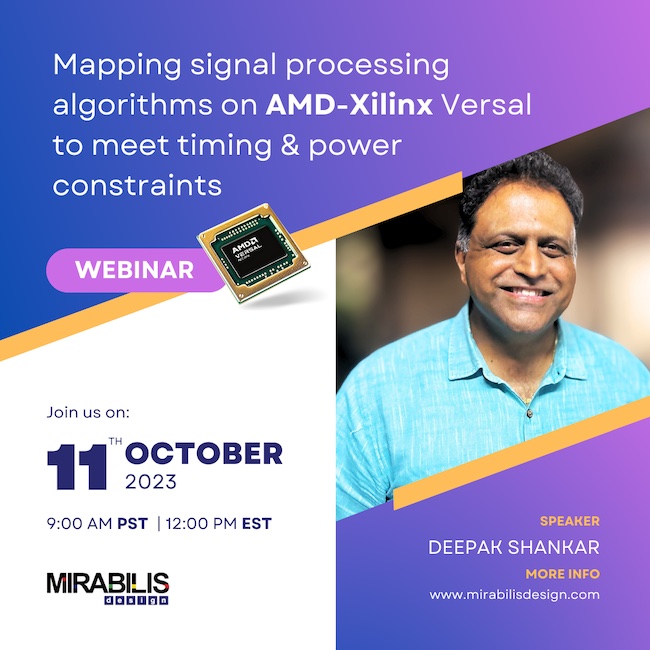

Mapping signal processing algorithms on AMD-Xilinx Versal to meet timing and power constraints

In this Webinar, we will focus on the performance-power-area trade-off in implementing signal processing algorithms on Xilinx FPGA by partitioning the tasks of the algorithms onto the processors, logic and AI Engines resident in the AMD-Xilinx Versal FPGA. Key Takeaways: Discover the inner workings of FPGA components: Processor, Logic Elements, AIE/Tensor, and more. Understand latency…

-

-

Achieve 95% Accurate Power Measurement during Architectural Exploration

Are you in the conceptualization and architectural exploration phases, where assessing the power budget is of paramount importance? If you're looking to achieve precise power measurement for critical aspects like embedded software, power management algorithms, hardware configurations, and more, this webinar is tailor-made for you. Webinar: How to achieve 95%+ Accurate Power Measurement during…

-

-

VLSID 2024

ITC Royal Bengal Kolkata, IndiaThe 37th International Conference on VLSI Design & the 23rd International Conference on Embedded Systems (VLSID 2024) are being held at Kolkata, India, during January 6-10, 2024. VLSID 2024 is returning to the city after 8 years since 2016. This flagship conference is bringing worldwide industry leaders, Indian and international industry bodies, and academic researchers in a…

-

-

Chiplet Summit

Santa Clara Convention Center 5001 Great America Parkway, Santa Clara, CA, United StatesThe Second Annual Chiplet Summit is the show chip designers can’t miss if they want to stay competitive. They’ll get the scoop on ways to make their chiplets run faster, scale better, use less power, and be more flexible. This unique event gives attendees a place to network with peers, ask questions of the experts,…

-

-

GOMACTech 2024

Embassy Suites by Hilton Charleston Convention Center, Charleston, SC, United StatesGOMACTech was established primarily to review developments in microcircuit applications for government systems. Established in 1968, the conference has focused on advances in systems being developed by the Department of Defense and other government agencies and has been used to announce major government microelectronics initiatives such as VHSIC and MIMIC, and provides a forum for…