- This event has passed.

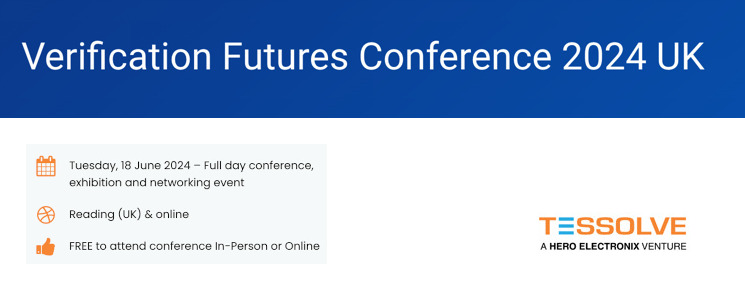

Verification Futures Conference 2024 UK

June 18 @ 8:30 am - 4:30 pm BST

The Verification Futures conference provides a unique blend of conference presentations, exhibitions, training and industry networking sessions dedicated to discussing the challenges faced in hardware and software verification. Verification Futures provides a unique opportunity for end-users to define their current and future verification challenges and collaborate with the vendors to create solutions. It also provides an excellent opportunity to network and catch up with other verification engineers and vendors from across Europe. Finally, we welcome students to encourage them on their first step into semiconductors as verification engineers.

Conference Program

| 08:30 | Arrival: Breakfast and Networking | Slides | Videos |

| 09:25 | Welcome: Mike Bartley, Tessolve Semiconductor Ltd | ||

| Keynote Speakers | |||

| 09:30 | The Ghosts of Challenges Past, Present and Future

Andy Bond (Axelera AI) |

||

| 10:05 | Presentation Title, Speaker name ( Company name) – TBC | ||

| 10:20 | Challenges of Developing Silicon for Automotive

Darren Galpin(UniSemi Power) |

||

| 10:30 | Presentation Title Speaker Name (Cadence) – Platinum Sponsor | ||

| 11:00 | Refreshments and Networking | ||

| Multi-Track Session (AM) | |||

| User presentations on Formal Verification | |||

| 11:30 | Presentation Title Speaker Name (Lubis EDA) – Start – up Sponsor | ||

| 11:50 | Presentation Title Speaker Name (Company Name) | ||

| 12:10 | Presentation Title Speaker Name (Company Name) | ||

| Track 2 – Student Session 1 – TBC | |||

| 11:30 | Presentation Title Speaker Name (Doulos) – Gold Sponsor | ||

| Track 3 – VHDL Verification- TBC | |||

| 11:30 | Presentation Title Speaker Name (Company Name) | ||

| 12:30 | Lunch and Networking | ||

| 13:30 | Presentation Title Speaker Name (Synopsys) – Platinum Sponsor (Keynote Speaker) | ||

| 14:00 | Presentation Title Speaker Name (Breker Verification Systems) – Gold Sponsor | ||

| 14:20 | Presentation Title Speaker Name (Company Name) – Gold Sponsor | ||

| 14:40 | Presentation Title Speaker Name (Company Name) | ||

| 15:00 | Refreshments and Networking | ||

| Multi-Track Session (PM) | |||

| Track 1 – Latest topics in Verification | |||

| 15:30 | Presentation Title Tom (Company Name) | ||

| 15:50 | Presentation Title Speaker Name (Company Name) | ||

| 16:10 | Presentation Title Speaker Name (Company Name) | ||

| Track 2 – Student Session 2- TBC | |||

| 15:30 | Presentation Title Speaker Name (Doulos) – Gold Sponsor | ||

| Track 3 – VHDL Verification – TBC | |||

| 15:30 | Presentation Title Speaker Name (Company Name) | ||

| Track 4 – UVM for MS Verification | |||

| 15:30 | Peter Grove (Renesas) | ||

| 16:30 | Event Closes |

A Semi-formal approach to coverage analysis and System-on-Chip debugging

– Dr. Surinder Sood, Principal Verification Engineer, ARM

The most challenging task in the System on Chip (SoC) development cycle is design validation and assurance that validation covers the entire design exhaustively, which is ensured using various coverage metrics. Due to tricky system level corner case scenarios, SoC coverage holes are observed. This coverage hole analysis can be done via multiple approaches. The most often used approaches are the tracker-based approach and the Waveform Dump (WD)-based approach. The issue with the tracker-based approach is that the trackers are not timing accurate and not always reliant due to many approximations in their generation flow.

Another approach is to debug and analyze using WD manually. WD with integrated tools like waveform debugger is extensively used for this purpose. The compute resources and time taken to launch signal dumps and debug the waveform are massive at the SoC-level and also lead to huge compute resources or lag in many cases. The lag time specifically, is of the order of hundreds of minutes in many cases. Consequently, SoC debug, micro-architectural analysis, and post-simulation analysis involves a lot of time and effort. We address this problem by developing an offline semi-formal approach that uses a temporal logic-based query mechanism.

This mechanism provides us to write system-level contracts which are decomposed of component-level guarantees. These are defined using Linear Temporal Logic (LTL) properties (called queries in this case) to Timed LTL and help realize an offline property justification framework. The proposed framework helps debug the failure using timed LTL queries on the WD and results are returned within a few seconds, consequently, making debugging easy. Moreover, this solution comes with a package of many allied benefits, which are described in the paper. We claim to improve the debug effort as we get a speedup of the order of 4x while debugging failed scenarios, as well as a significant improvement in coverage analysis.

3 Key Points

- Linear Temporal logic

- Formal verification

- System on Chips