IP

Events

-

-

How to Overcome the Pain Points of AI/ML Hardware Design

Join Achronix for a live Webinar December 16th: 10-11 AM Pacific and Recorded On-Demand After the Event AI/ML hardware faces three common pain points: memory bandwidth, computational throughput and on-chip data movement. Next-generation FPGA technology includes a 2D network on chip, GDDR6 memory interfaces and high performance machine learning processors, which present new capabilities to… How to Overcome the Pain Points of AI/ML Hardware Design

-

-

Boost Your CXL Verification from IP to System Level

Register now for this CadenceTECHTALK, where we will walk you through CXL verification challenges from IP level to system level and demonstrate how these challenges can be significantly mitigated using the Cadence® Verification IP (VIP) solution for advanced verification methodologies. Specifically, this webinar will cover following topics: Growing market needs for CXL Verification challenges of… Boost Your CXL Verification from IP to System Level

-

-

ASIP Virtual Seminar 2022

Extending RISC Processors into Flexible Accelerators using ASIP Designer Case Studies in Artificial Intelligence and Image Signal Processing The slow-down of Moore’s law and Dennard scaling has triggered an increased awareness of application-specific instruction-set processors (ASIPs). These processors implement a specialized instruction-set architecture (ISA) tailored to the application domain, often starting from a baseline such… ASIP Virtual Seminar 2022

-

Managing the Complexity of FinFET Standard Cell Layout with Cello

FinFET technologies have enabled designs with increased density and performance while reducing power, when compared to MOSFET. However, this comes at a cost of increased design complexity. Not only are some undesirable layout dependent effects more pronounced, but design rules have become much more complex. Many design rules violations can no longer be fixed within… Managing the Complexity of FinFET Standard Cell Layout with Cello

-

Optimized Chip Design with Main Processors and AI Accelerators

Presented by Paul Karazuba, VP of Marketing, Expedera & John Min, Director of Field Application Engineering, Andes Technology About this talk As AI capability is beginning large-scale deployment into edge devices, many wonder about the decision to use a specialized AI accelerator, rather than simply using the systems main processor. In this first of two… Optimized Chip Design with Main Processors and AI Accelerators

-

SemIsrael Tech Webinar

SemIsrael Expo is the premier professional semiconductor event in Israel. The event brings together hundreds of Israeli semiconductor professionals from all fields and aspects of the semiconductor industry. The Expo will host some 750 semiconductor professionals from all the Israeli semiconductor community; local fabless & startups, local R&D offices of multinationals and IDMs, foundries, design… SemIsrael Tech Webinar

-

The Role of PUFs in a Trusted Supply Chain

Trusted supply chain provenance and traceability is becoming increasingly important for the quality, reliability, and security of electronic products. It can help reduce costs for tracking and fixing field issues, minimize liability risks and enable higher value in connected IoT applications. In addition, there are significant efficiencies and cost reductions that could be enabled in… The Role of PUFs in a Trusted Supply Chain

-

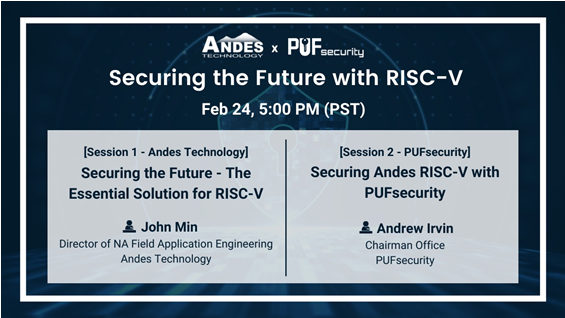

Securing the Future with RISC-V

While the metaverse took the spotlight at the recent CES, it is made possible with advancement in computation and connectivity, which also empower many other aspects of people's lives from IoT, Automotive, and to all kinds of applications around us. While Andes RISC-V has continued to enable innovations in all emerging applications, security in modern SoC… Securing the Future with RISC-V

-

-

Spatial Audio: What it is and how to overcome its unique challenges to provide a complete solution

Audiovisual experiences in XR, gaming, movies, and concerts can all be enhanced with spatial audio experience immersive technology. A superior spatial audio experience occurs when you combine headphones, with wearable head tracking, and on-device processing. Believe it or not, despite the recent wide adoption of Spatial/3D Audio, the concept and technology have been around for a… Spatial Audio: What it is and how to overcome its unique challenges to provide a complete solution

-

Balancing Performance and Power in adding AI Accelerators to System-on-Chip (SoC)

• Do you need to estimate the power advantage of implementing an AI algorithm on an accelerator? • Do you need to size the AI accelerator for existing and future AI requirements? • Would it be beneficial if you knew the latency advantage between ARM, RISC, DSP and Accelerator in deploying AI tasks? This webinar… Balancing Performance and Power in adding AI Accelerators to System-on-Chip (SoC)

-

Power Intent Management for Large SoCs

Defacto Techologie 2 rue Emile Augier, Grenoble, FranceThe complexity of system on chips keeps increasing and SoC designers keep having lot of pressure to deliver and keeping the cost as low as possible. To stay within a PPA budget (power performance area), it's challenging daily for designers. Defacto’s SoC Compiler keep providing innovative solutions to increase the productivity of designers. During this… Power Intent Management for Large SoCs

-

Memory Bandwidth Races Higher with HBM3

With the formal release of the HBM3 specification, memory bandwidth for AI/ML and HPC shifts to a higher gear. Terabytes of bandwidth are possible using HBM3’s 2.5D/3D architecture. Join memory expert Frank Ferro as he discusses what changes come with the new generation of HBM, and how the Rambus HBM3 memory subsystem can help designers… Memory Bandwidth Races Higher with HBM3