Doulos

Events

-

-

Dealing with Complexity in Formal through Abstraction and Reduction

In the world of formal verification, abstractions along with design reductions, help reduce the state space and make it easier for formal to converge on its proofs. In this webinar Doulos Senior Member Technical Staff, Doug Smith will explore the process of abstraction, safe design reductions, and when to use them. Doug will show practical…

-

-

Dealing with Inconclusive Formal Proofs

Webinar Overview: Formal proofs of end-to-end properties can be a very valuable contribution to RTL sign-off and yet are often the most difficult to achieve. In this webinar Doulos Senior Member Technical Staff, Doug Smith will explore some practical ways of dealing with inconclusive formal proofs when using Jasper by Cadence . This includes the…

-

-

Everything You Need to Know about SystemVerilog Arrays

This webinar gives a comprehensive guide to all aspects of SystemVerilog arrays: ordinary static arrays, dynamic arrays, queues and associative arrays. It also includes array methods and practical examples. Topics: Review of Verilog array types SystemVerilog packed and unpacked arrays SystemVerilog dynamic arrays SystemVerilog queues SystemVerilog associate arrays Array manipulation methods. Coding examples are shown…

-

Verification Futures 2023 Austin

Austin Marriott South 4415 South Interstate 35 Frontage Road, Austin, TX, United StatesThe Verification Futures conferences is dedicated to discussing the challenges faced in hardware and software verification. To view the agenda for this event please visit the VF2023 Event Page. The full conference program includes 17 talks covering verification challenges and solutions, formal verification, RISC-V, System Verilog, UVM for AMS Verification, and VHDL Verification View the full conference…

-

Maximize Design Productivity using Vivado ML with SystemVerilog

Although SystemVerilog is perhaps most widely used in the context of hardware verification, it also contains many features directly relevant to FPGA hardware designers. We explore the features of SystemVerilog that are useful for RTL synthesis using Vivado™ ML Editions from AMD, showing how the RTL SystemVerilog language constructs have been optimized for productivity and reliability.…

-

-

Deep Dive into the UVM Register Layer: User-Defined Doors, Predictors, and Callbacks

This webinar focuses on three specific aspects of the UVM register layer that will help you to model in UVM some of the less obvious ways in which registers can behave, such as non-linear addressing, burst access mode, registers accessed through an embedded CPU, and quirky registers. It will cover the following topics: Using user-defined…

-

-

Debugging SystemC with GDB

Webinar Overview: This webinar explores debugging SystemC code with basic tools, including issues and strategies to make improvements. A large portion of the webinar includes a demonstration of a small design. Topics include single-stepping without getting lost and obtaining information about SystemC simulation status. The session concludes with ideas on how to simplify debugging and…

-

-

DVCon USA 2024

The DoubleTree by Hilton 2050 Gateway Place, San Jose, CA, United StatesThe Design & Verification Conference & Exhibition is the premier conference on the application of languages, tools, methodologies and standards for the design and verification of electronic systems and integrated circuits. The focus of this highly technical conference is on the practical aspects of these technologies and their use in leading-edge projects to encourage attendees…

-

-

Debugging Features of UVM

A UVM testbench is a large and complex piece of software. Like any other large and complex piece of software, a verification environment written using UVM will require debugging at some stage. There are various debugging features built into UVM to help with this. In this one-hour webinar, Doulos Senior Member Technical Staff Doug Smith…

-

-

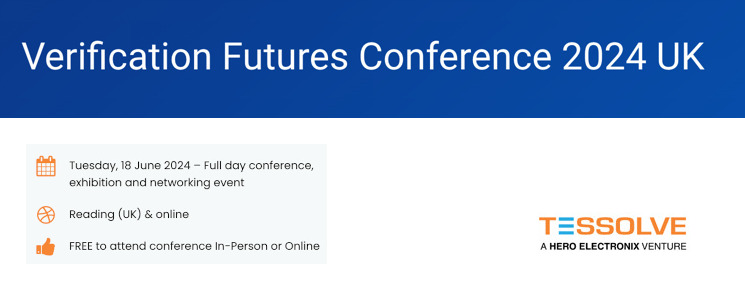

Verification Futures Conference 2024 UK

The Verification Futures conference provides a unique blend of conference presentations, exhibitions, training and industry networking sessions dedicated to discussing the challenges faced in hardware and software verification. Verification Futures provides a unique opportunity for end-users to define their current and future verification challenges and collaborate with the vendors to create solutions. It also provides…

-

-

Verification Futures Conference 2024 Austin

Austin Marriott South 4415 South Interstate 35 Frontage Road, Austin, TX, United StatesThe Verification Futures conference provides a unique blend of conference presentations, exhibitions, training and industry networking sessions dedicated to discussing the challenges faced in hardware and software verification. Verification Futures provides a unique opportunity for end-users to define their current and future verification challenges and collaborate with the vendors to create solutions. It also provides…

-

-

DVCON US 2025

The DoubleTree by Hilton 2050 Gateway Place, San Jose, CA, United StatesThe Design & Verification Conference & Exhibition is the premier conference on the application of languages, tools, methodologies and standards for the design and verification of electronic systems and integrated circuits. The focus of this highly technical conference is on the practical aspects of these technologies and their use in leading-edge projects to encourage attendees…