Synopsys

-

-

What’s Needed to Perform End-to-End Testing for 5G Open Radio Access Network SoCs

Testing an O-RAN Radio Unit (O-RU) SoC at full scale implies sending realistic traffic, in conformance with current specifications and at the right time on the right interfaces to simulate complex scenarios and cover as many corner cases as possible. It requires a robust debug methodology which can provide quick turn around and appropriate window… What’s Needed to Perform End-to-End Testing for 5G Open Radio Access Network SoCs

-

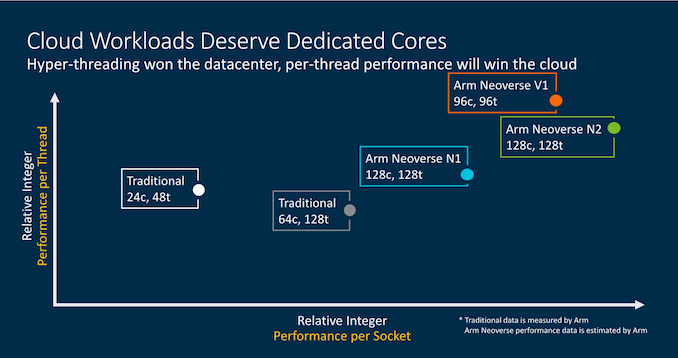

A Scalable Approach to 2X Faster Turnaround Time for Arm Neoverse N2 Core Design Verification

In the latest generation of multiple processor SoCs, designers are adding cache-coherent agents beyond the multi-processor clusters, making it a complex verification challenge. System coherency needs to be maintained at various levels, beginning at the cluster level, and continuing, across the cache coherent interconnect and across chips through chip-to-chip gateways. The coherency protocol across interconnects… A Scalable Approach to 2X Faster Turnaround Time for Arm Neoverse N2 Core Design Verification

-

Accelerate Semiconductor Technology Development and Innovation

Seminar Overview Join our online TCAD Seminar to learn about the application of Synopsys TCAD solutions to accelerate the research, development and optimization of semiconductor technologies. The seminar tracks cover all major semiconductor technologies, from advanced logic and memory to analog, power and optoelectronics. The solutions presented in this seminar are based on the industry-standard… Accelerate Semiconductor Technology Development and Innovation

-

Everything you wanted to know about VHDL configurations

VHDL configurations are a much maligned, much ignored part of the VHDL language. Consequently, many VHDL designers find them quite scary. This webinar seeks to answer the questions you may not have had answered in the past; shedding light on the mystery of VHDL configurations and showing a practical example of how to apply them,… Everything you wanted to know about VHDL configurations

-

-

IP-SoC Conference 21

IP-SoC 2021 will be the 24th edition of the working conference fully dedicated to IP (Silicon Intellectual Property) and IP based electronic systems. The event is the annual opportunity for IP providers and IP consumers to share information about technology trends, innovative IP SoC products, Breaking IP/SoC News, Market evolution and more. The Grenoble event is… IP-SoC Conference 21

-

PCIe 6.0 From IP to Interconnect in High-Performance Computing

ABSTRACT: PCI Express (PCIe) is one of the most popular interface technologies in the world. Interconnects for high-performance computing (HPC) in the data center, cloud and AI edge continue to increase in speed and density. System architects, SoC designers, PCB developers and SI engineers are challenged as never before to implement bleeding edge solutions. In… PCIe 6.0 From IP to Interconnect in High-Performance Computing

-

DVCON India

This conference will give you ample opportunities to share and highlight your technical contibutions in the areas of Verificaiton and Validations, Methodology & Automation, Functional Safety & Security, Low Power and Mixed Signal Design, Static and Formal methods and Digital Twins and SystemC Modeling. Kindly use this opportunity and register yourself for the conference.… DVCON India

-

-

Improving Design Power and Performance with RTL Architect

Exploring the impact of RTL on implementation PPA has traditionally been very difficult since it was hard to connect the results to the source code. The first difficulty occurs during elaboration and synthesis. The RTL is converted to gates and the references to the source code are lost. The second difficulty is the gate-centric, implementation, PPA reports.… Improving Design Power and Performance with RTL Architect

-

-

ASIP Virtual Seminar 2022

Extending RISC Processors into Flexible Accelerators using ASIP Designer Case Studies in Artificial Intelligence and Image Signal Processing The slow-down of Moore’s law and Dennard scaling has triggered an increased awareness of application-specific instruction-set processors (ASIPs). These processors implement a specialized instruction-set architecture (ISA) tailored to the application domain, often starting from a baseline such… ASIP Virtual Seminar 2022

-

Exploring a Software First Approach to Avoid SoC Re-spins

Traditional coverage-based verification methods are no longer sufficient to verify complex SoCs integrating many processor cores and IP subsystems. To conquer the verification challenge of complex SoCs, companies are shifting their development paradigm to a software first approach. By considering the target software up front, as a critical part of the SoC development process, designs… Exploring a Software First Approach to Avoid SoC Re-spins

-

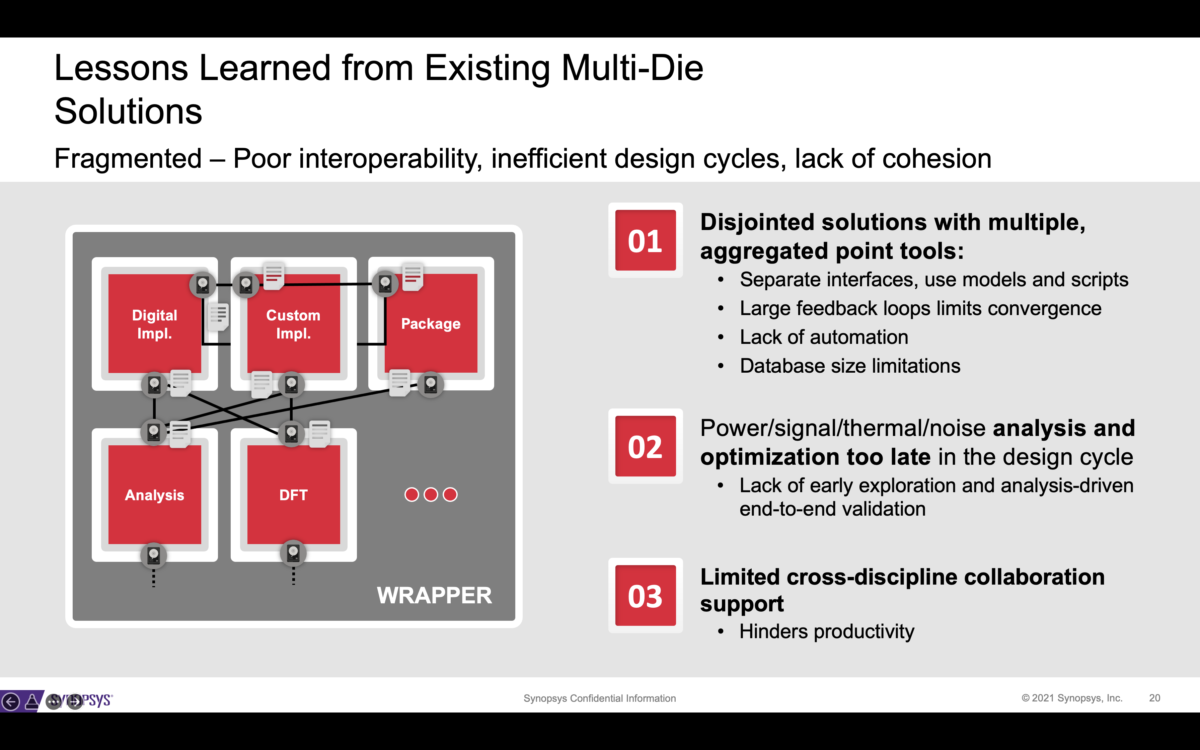

3DIC Design from Concept to Silicon

For some high-performance computing (HPC) designs, monolithic SoCs aren’t producing the scalability and yield that designers are looking for. New trends towards 3DIC design are emerging introducing new design challenges, such as reliable die-to-die connectivity, high bandwidth memory, integration, and 2.5D or 3D packaging options. This webinar will outline the different market trends for 3DIC… 3DIC Design from Concept to Silicon

-

SemIsrael Tech Webinar

SemIsrael Expo is the premier professional semiconductor event in Israel. The event brings together hundreds of Israeli semiconductor professionals from all fields and aspects of the semiconductor industry. The Expo will host some 750 semiconductor professionals from all the Israeli semiconductor community; local fabless & startups, local R&D offices of multinationals and IDMs, foundries, design… SemIsrael Tech Webinar