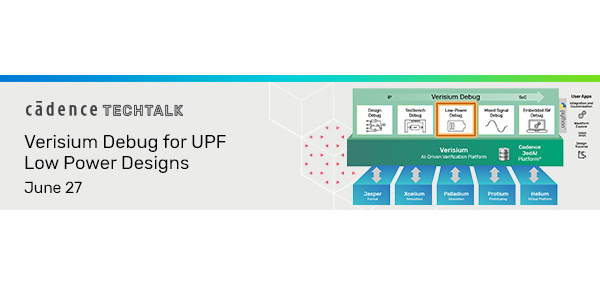

Verisium Debug for UPF Low Power Design

Verisium Debug offers comprehensive debugging capabilities. From RTL, UVM testbench to UPF low-power designs, users can use the Cadence unified debugging platform for debugging. In this webinar, users will learn about the available features in…