-

-

Embedded Vision Summit 2023

Santa Clara Convention Center 5001 Great America Parkway, Santa Clara, CA, United StatesThe Summit attracts a global audience of technology professionals from companies developing computer vision and edge AI-enabled products including embedded systems, cloud solutions and mobile applications. Why attend? It's a First-Rate Program with Powerful Insights into Practical Perceptual AI. Join us for four days of learning—from tutorials to deep-dive days, covering the latest technical insights,… Embedded Vision Summit 2023

-

Extending RISC Processors into Flexible Accelerators using ASIP Designer

Case Studies in Low-Power Smart Vision and Post-Quantum Cryptography Applications The slow-down of Moore’s law and Dennard scaling triggered an increased awareness for application-specific instruction-set processors (ASIPs). These processors implement a specialized instruction-set architecture (ISA) tailored to the application domain, often starting from a baseline such as the RISC-V ISA. ASIPs can replace traditional fixed-function… Extending RISC Processors into Flexible Accelerators using ASIP Designer

-

DENSO discusses Verification of network relay performance using VisualSim

Want to learn how Tier One suppliers are using network modeling and simulation in the design and optimization of network topology and gateway architecture. Then attend this Webinar by DENSO. Efficient in-vehicle network development through simulation combining network and ECU hardware and software elements Time Zone: Japan - 3:00 PM (In Japanese) Asia - 3:00… DENSO discusses Verification of network relay performance using VisualSim

-

Advancing MRAM Technology with Atomistic Spin Dynamics Simulations

In this event, experts from Martin-Luther-Universitat Halle Wittenberg, University of York, and Synopsys QuantumATK will present how to use ab initio DFT modeling and atomistic spin dynamics simulations of MTJs to guide and accelerate the technological development of magnetic memory such as STT and SOT-MRAM. Investigating the potential of novel magnetic tunnel junction (MTJ) materials… Advancing MRAM Technology with Atomistic Spin Dynamics Simulations

-

Requirements for Multi-Die System Success

Wednesday, May 24, 2023 and Thursday, May 25, 2023 The industry is moving to multi-die systems to benefit from the greater compute performance, increased functionality, and new levels of flexibility. Challenges for multi-die systems are exacerbated and require greater focus on a number of requirements such as early partitioning and thermal planning, die/package co-design, secure… Requirements for Multi-Die System Success

-

Accelerate Coverage Closure and Debug with Synopsys AI-Driven Verification Solutions

Synopsys Webinar | Wednesday, May 24, 2023 | 10:00 - 10:45 a.m. IST Engineering resources are getting stretched thinner and thinner as design complexity increases. Automation is a significant driver to help engineers overcome resource constraints and meet critical time-to-market windows. Two of the top three challenges cited by the engineering community in a recent… Accelerate Coverage Closure and Debug with Synopsys AI-Driven Verification Solutions

-

Don’t Take the Risk, Formally Verify Your RISC-V Cores

Synopsys Webinar | Thursday, May 25, 2023 | 9:00 a.m. PT According to a recent Semico Research report, the RISC-V Core IP market is expected to grow at a 34.9% CAGR through year 2027. With increasing popularity, it is of utmost importance that the RISC-V Core IPs are secure and bug free. In this… Don’t Take the Risk, Formally Verify Your RISC-V Cores

-

SiFive Maximizes Compute Density With Its RISC-V Processor Cores

IP vendor SiFive has been at the forefront of RISC-V’s rapidly growing adoption across a wide array of markets and applications. In this joint presentation with Ansys, SiFive will describe how achieving maximum compute density - compute horsepower per mm2 and per mW (e.g SPECint2006/mm2) - has been a driving goal for SiFive’s portfolio of… SiFive Maximizes Compute Density With Its RISC-V Processor Cores

-

STAC Summit

New York Marriott Marquis 1535 Broadway, New York City, NY, United StatesSTAC Summits bring together CTOs and other industry leaders responsible for solution architecture, infrastructure engineering, application development, machine learning/deep learning engineering, data engineering, and operational intelligence to discuss important technical challenges in trading and investment.

-

-

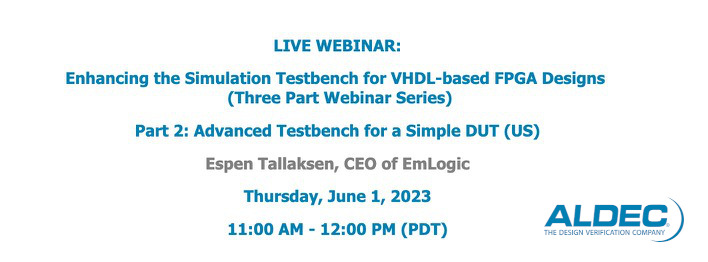

Advanced Testbench for a Simple DUT

Abstract: Functional simulation using an HDL testbench is the de facto method for proving functional correctness of FPGA designs. In this three-part webinar series, we will present a step-by-step approach on how to architect a testbench - progressing from basic to advanced techniques. We will first use a simple DUT then go to a more… Advanced Testbench for a Simple DUT

-

Accelerate Software Innovation Through Target-Optimized Code Generation and Virtual Prototypes

Increasingly complex automotive systems are driving the need for new and powerful E/E architectures, and new technology is emerging that offers a significant computational increase compared to previous generation SoCs. To deliver next-generation, differentiated software solutions, model-based design (MBD) workflows must be deployed to handle this new level of complexity. Code generation solutions that optimize… Accelerate Software Innovation Through Target-Optimized Code Generation and Virtual Prototypes

-

Xcelium: The Key to Unlocking Unmatched Mixed-Signal Performance

Xcelium mixed-signal simulation enables teams to achieve digital simulation speeds of analog models and opens mixed-signal designs to advanced verification techniques typically applied within standard verification flows. Built on a SystemVerilog Real Number Modeling (RNM) foundation, Xcelium automates the signal integration of digital and RNM code to achieve digital simulation speeds for mixed-signal designs. This… Xcelium: The Key to Unlocking Unmatched Mixed-Signal Performance

12 events found.