-

Flash Memory Summit

Santa Clara Convention Center 5001 Great America Parkway, Santa Clara, CA, United StatesProgram It is ideal for consumer applications such as cellphones, digital cameras, and music players, and is also useful in computers, communications systems, and military/defense applications. It can replace hard… Flash Memory Summit

-

Advanced Physical Design using OpenLANE/Sky130

Physical Design or PnR (Place and Route) is the core of any IC design cycle. From a RTL netlist to final tape-out, each phase of PnR brings it’s own challenges… Advanced Physical Design using OpenLANE/Sky130

-

A Smart and Automatic Assembly and Connections for SoCs

Learn how to automatically assemble and connect IPs from many different sources at your SoC level using SoC Enterprise™. This includes automatic generation of components such as aggregators, bridges, channels,… A Smart and Automatic Assembly and Connections for SoCs

-

2022 R2: What’s New in Ansys Signal & Power Integrity

About this Event The 2022 R2 Ansys Signal and Power Integrity release introduces significant simulation improvements for electronic printed circuit boards, IC packages, and interposers. Ansys SIwave delivers new features,… 2022 R2: What’s New in Ansys Signal & Power Integrity

-

Has the Time for Analog Automation Finally Come?

The semiconductor industry is experiencing explosive growth, driven by emerging applications such as AI, 5G, IoT and automotive. To keep pace, design teams have deployed sophisticated CAD tools that can… Has the Time for Analog Automation Finally Come?

-

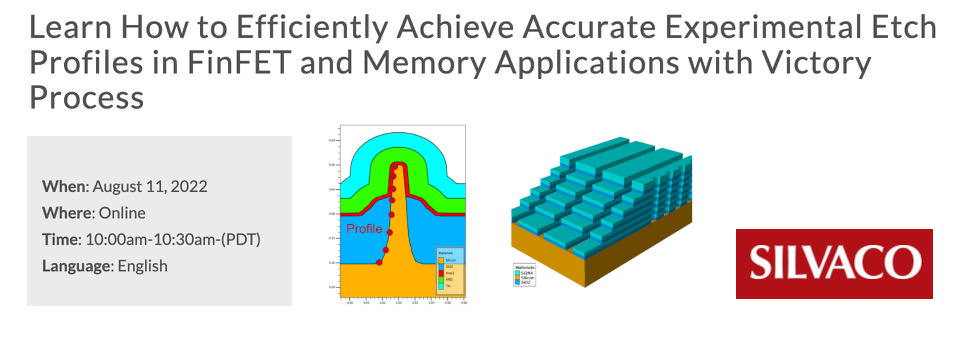

Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

When employing process simulation to generate a complex device structure, TCAD engineers often face the task of reproducing the exact etch profile that has been observed in semiconductor fabrication. Silvaco… Learn How to Efficiently Achieve Accurate Experimental Etch Profiles in FinFET and Memory Applications with Victory Process

-

CAD for Assurance: Panel 5: Hardware Assurance vs. AI: Friend or Foe?

Moderators: Ankur Srivastava (U. of Maryland) and Swarup Bhunia (U. of Florida) Panelists: - Mike Borza, Synopsys - Brian Night, Microsoft - Pompei Len Orlando, Air Force Research Lab (AFRL)… CAD for Assurance: Panel 5: Hardware Assurance vs. AI: Friend or Foe?

-

Fast and Accurate Functional ECOs with Synopsys Formality ECO

To achieve maximal quality of results (QoR) in synthesis, it requires leveraging retiming, multibit banking, and advanced datapath optimizations, which are part of the Synopsys Fusion Compiler™ implementation solution. However,… Fast and Accurate Functional ECOs with Synopsys Formality ECO

-

Sustainability for Semiconductors

Don’t miss your chance to join this important conversation with industry leaders that are making an impact on the reduction of the semiconductor carbon footprint. Donna Yasay Senior Leader, Solutions… Sustainability for Semiconductors

-

FPGAs for AI and AI for FPGAs

Artificial Intelligence (especially Deep Learning) is rapidly becoming the cornerstone of numerous applications, creating an ever-increasing demand for efficient Deep Learning (DL) processing. FPGAs provide massive parallelism, while being flexible… FPGAs for AI and AI for FPGAs

-

Design and Verify State-of-the-Art RFICs using Synopsys / Ansys Custom Design Flow

Wireless communication is at the heart of the technological revolution of the past few decades and RF circuits are what enable wireless systems to communicate with each other. The design… Design and Verify State-of-the-Art RFICs using Synopsys / Ansys Custom Design Flow

-

A Key principle to successful tape-outs for Cadence Virtuoso users 10am PDT

As working remotely and virtually has become the new norm, collaboration and coordination between colleagues has its challenges and its obstacles. If you are using Cadence Virtuoso and working on… A Key principle to successful tape-outs for Cadence Virtuoso users 10am PDT

12 events found.