-

-

Zero Trust Supply Chains and the Risk of Gray Market Chips

The recent shortage of chip supply and long lead times prompted system makers to turn to second tier suppliers and distributors for fulfilling their semiconductor needs. This in turn has put a spotlight on the growing concern of fraudulent or counterfeited Integrated Circuits (ICs). This webinar will discuss challenges and new approaches to supply chain… Zero Trust Supply Chains and the Risk of Gray Market Chips

-

Exploring a Software First Approach to Avoid SoC Re-spins

Traditional coverage-based verification methods are no longer sufficient to verify complex SoCs integrating many processor cores and IP subsystems. To conquer the verification challenge of complex SoCs, companies are shifting their development paradigm to a software first approach. By considering the target software up front, as a critical part of the SoC development process, designs… Exploring a Software First Approach to Avoid SoC Re-spins

-

Accelerate Innovation with the Omnis Automotive Wizard for CFD Simulations

Overview There is no time to waste in the automotive industry, where time to market is less than a year these days. That’s one of the reasons computational fluid dynamics (CFD) simulation has become crucial in automotive design, as it enables engineers to accurately predict and understand real-world behavior of their vehicles early in the… Accelerate Innovation with the Omnis Automotive Wizard for CFD Simulations

-

Managing the Complexity of FinFET Standard Cell Layout with Cello

FinFET technologies have enabled designs with increased density and performance while reducing power, when compared to MOSFET. However, this comes at a cost of increased design complexity. Not only are some undesirable layout dependent effects more pronounced, but design rules have become much more complex. Many design rules violations can no longer be fixed within… Managing the Complexity of FinFET Standard Cell Layout with Cello

-

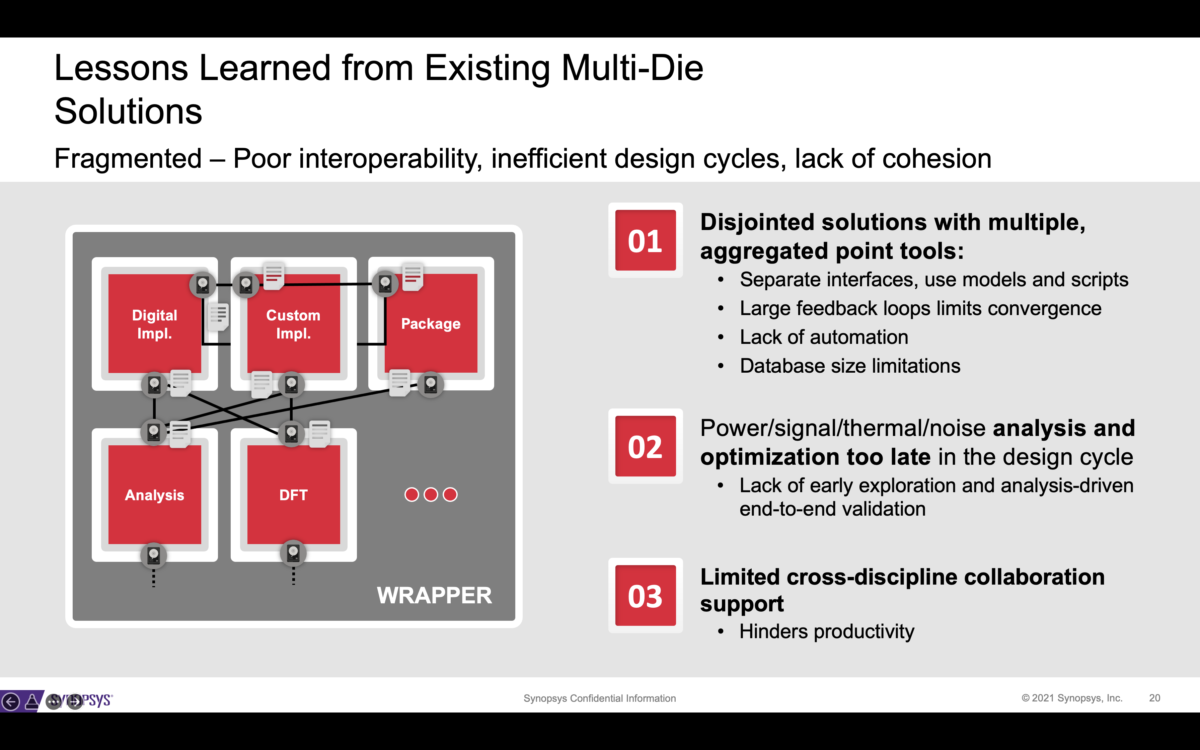

3DIC Design from Concept to Silicon

For some high-performance computing (HPC) designs, monolithic SoCs aren’t producing the scalability and yield that designers are looking for. New trends towards 3DIC design are emerging introducing new design challenges, such as reliable die-to-die connectivity, high bandwidth memory, integration, and 2.5D or 3D packaging options. This webinar will outline the different market trends for 3DIC… 3DIC Design from Concept to Silicon

-

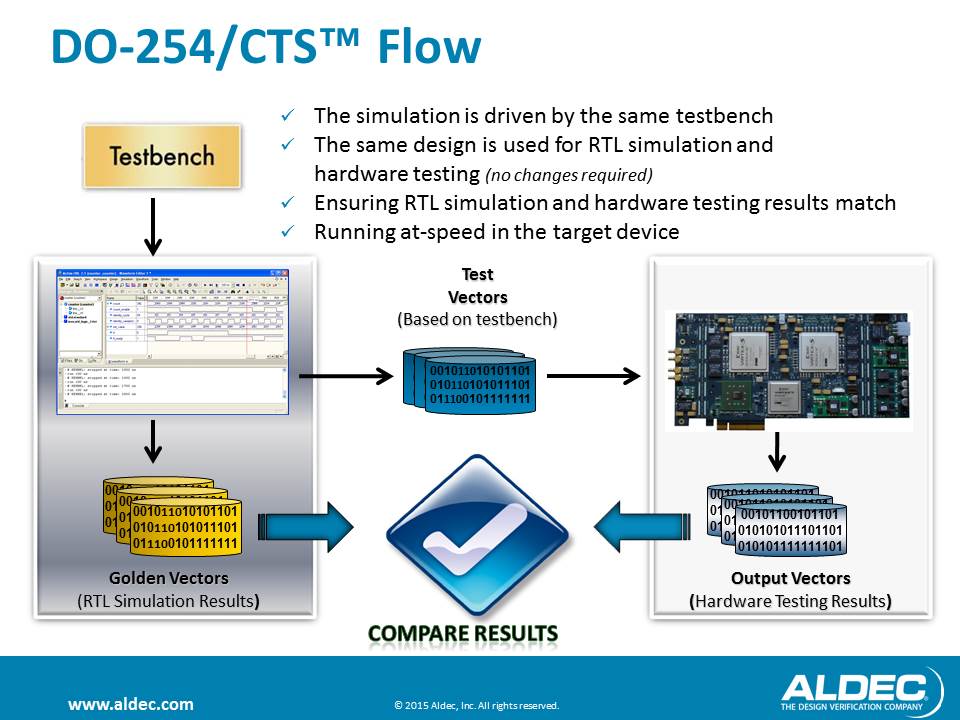

Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance (US)

PCIe-based FPGA designs are becoming popular within avionics systems. However, the verification of such designs for DO-254 compliance with design assurance level (DAL) A or B is problematic. FPGA designs that use asynchronous clocks with multiple high-speed serial interfaces such as PCIe produce non-deterministic results during physical tests. Simulation results are optimized because they are… Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance (US)

-

ACCELERATE PACKAGE THERMAL MODELING IN ELECTRONICS COOLING DESIGN WEBINAR

How do you generate faster, accurate semiconductor package thermal models? This webinar focuses on thermal modeling of electronics packages to predict component temperature in system-level electronics cooling simulations during development. From semiconductor device OEMs supporting the electronics supply chain to engineers selecting and integrating components into electronics product, it is important to have appropriate accuracy… ACCELERATE PACKAGE THERMAL MODELING IN ELECTRONICS COOLING DESIGN WEBINAR

-

Optimized Chip Design with Main Processors and AI Accelerators

Presented by Paul Karazuba, VP of Marketing, Expedera & John Min, Director of Field Application Engineering, Andes Technology About this talk As AI capability is beginning large-scale deployment into edge devices, many wonder about the decision to use a specialized AI accelerator, rather than simply using the systems main processor. In this first of two… Optimized Chip Design with Main Processors and AI Accelerators

-

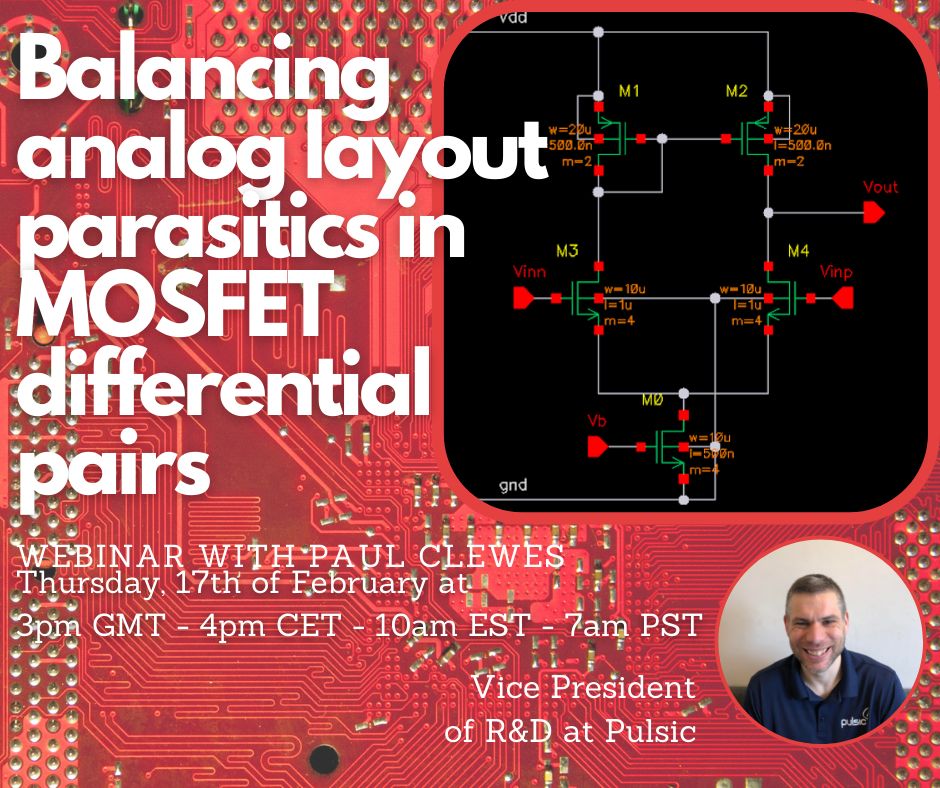

Balancing analog layout parasitics in MOSFET differential pairs

The MOSFET differential pair is a key part of many analog circuits e.g. opamps, comparators, LDOs, etc. A differential pair applies gain to the difference between two signals and has many advantages over single-ended amplifier circuits, e.g. noise reduction and suppression of common-mode signals and DC offset. However, these advantages rely upon precisely matched circuit… Balancing analog layout parasitics in MOSFET differential pairs

-

How to Improve Physical Verification Productivity with SmartDRC/LVS

Physical Verification is the most critical stage of IC design. SmartDRC/LVS is a new physical verification tool for analog, digital and mixed-signal ICs including design rule checks (DRC), layout connectivity extraction and layout vs schematic (LVS) comparisons. Its unique multi-CPU architecture delivers high performance and capacity, accurate processing of complex shapes, and exceptional user productivity… How to Improve Physical Verification Productivity with SmartDRC/LVS

-

Open-Source FPGA: Towards Fully Automated FPGA Tapeout Flows

In this webinar, we will present the open-source FPGA tools which automate the tapeout flow for custom FPGA fabrics. We will cover the key steps involved in the process when using the tools, including netlist generation, design verification and performance prediction. We will also introduce the latest features in open-source FPGA and explain how they… Open-Source FPGA: Towards Fully Automated FPGA Tapeout Flows

-

Mixed-Signal SoC Verification Simplified with Xcelium Simulator

Analog and mixed-signal verification has always been a challenge for design and verification engineers. It has become tedious with the increasing complexity of SoC designs. Because the analog behavior of key design blocks cannot be simulated effectively using traditional verification methodologies, new methodologies and solutions like real number modeling (RNM) for analog functional blocks are… Mixed-Signal SoC Verification Simplified with Xcelium Simulator

12 events found.