Webinar

Constraint Random Verification with Python and Cocotb

Abstract: Testing digital hardware has never been an easy job, and it won’t get easier any time soon. But that doesn’t mean writing test code can’t be enjoyable and productive!… Read More »Constraint Random Verification with Python and Cocotb

Boost LPDDR5 Verification from IP to System Level

Overview Low power DRAM is being adopted in a wide array of markets, including automotive, PCs and networking systems built for 5G and AI applications. The specification complexity is increasing… Read More »Boost LPDDR5 Verification from IP to System Level

CXL and IDE: Important Considerations of Protecting High Speed Interconnects

In a few short years, CXL (Compute Express Link) has evolved from an idea to a rapidly proliferating low latency interconnect standard being adopted into data centers, high performance computing,… Read More »CXL and IDE: Important Considerations of Protecting High Speed Interconnects

Workforce Shortages—Meeting Challenges for the Semiconductor Industry

As demand for semiconductors is increasing, foundries and other makers of chips are expanding their manufacturing capacities. With new fabs bringing thousands of new jobs to the US, Texas is… Read More »Workforce Shortages—Meeting Challenges for the Semiconductor Industry

Virtual Prototyping Day – Silver: Accelerate Your Innovation with Virtual ECUs

Synopsys invites you to the Virtual Prototyping Day – Silver, a virtual event on virtual ECUs and applications in automotive software development. Users share their experiences with the latest techniques… Read More »Virtual Prototyping Day – Silver: Accelerate Your Innovation with Virtual ECUs

Enabling Effective Design & Layout Collaboration for Next Generation Analog and Mixed-Signal Designs

Analog designers appreciate the importance of tight communication between layout and design teams, yet with geographically dispersed teams this can be a big challenge. Close collaboration between circuit designer and… Read More »Enabling Effective Design & Layout Collaboration for Next Generation Analog and Mixed-Signal Designs

The Evolution of Process TCAD in Semiconductor R&D and Manufacturing

Shela Aboud, Ph.D., Synopsys Today, nearly every aspect of an integrated circuit is designed using EDA software. Technology computer aided design (TCAD) tools are used for modeling front-end-of-line manufacturing, including… Read More »The Evolution of Process TCAD in Semiconductor R&D and Manufacturing

What’s Needed to Perform End-to-End Testing for 5G Open Radio Access Network SoCs

Testing an O-RAN Radio Unit (O-RU) SoC at full scale implies sending realistic traffic, in conformance with current specifications and at the right time on the right interfaces to simulate… Read More »What’s Needed to Perform End-to-End Testing for 5G Open Radio Access Network SoCs

Practical Flows for Continuous Integration: Making The Most of Your EDA Tools

Verifying changes to RTL and testbench code prior to releasing to the rest of your team is the best way to avoid committing bugs that cause massive, team-wide disruptions. This… Read More »Practical Flows for Continuous Integration: Making The Most of Your EDA Tools

Accelerating Analog Layout

The growing demand for analog features on IoT devices means that analog designers are under constant pressure to complete more designs faster than ever. For most layout designers, analog layout… Read More »Accelerating Analog Layout

CadenceTECHTALK: Power and Energy Optimization Using Tensilica IP

Join us as Cadence experts describe common challenges and solutions in creating an efficient and accelerated flow that will meet technical requirements for accurately measuring the power, energy, and system… Read More »CadenceTECHTALK: Power and Energy Optimization Using Tensilica IP

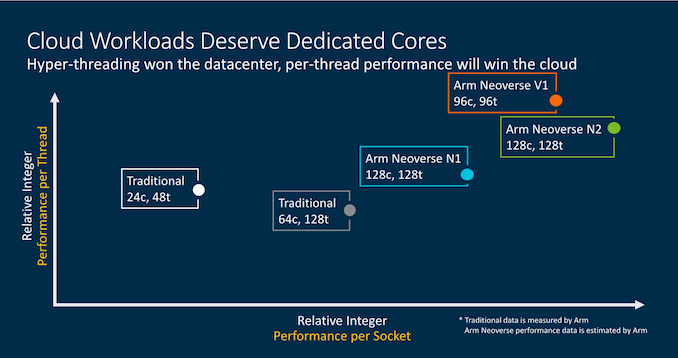

A Scalable Approach to 2X Faster Turnaround Time for Arm Neoverse N2 Core Design Verification

In the latest generation of multiple processor SoCs, designers are adding cache-coherent agents beyond the multi-processor clusters, making it a complex verification challenge. System coherency needs to be maintained at… Read More »A Scalable Approach to 2X Faster Turnaround Time for Arm Neoverse N2 Core Design Verification