3D IC

Events

-

-

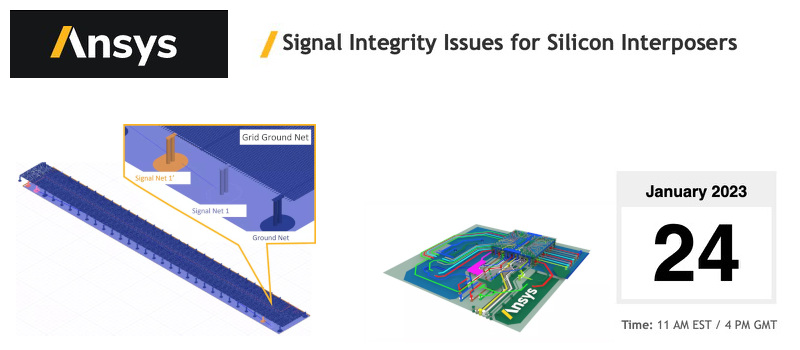

Signal Integrity Issues for Silicon Interposers

The development of applications like high-performance computing, Artificial Intelligence (AI) processors, and Central Processing Unit (CPU) and Graphical Processing Unit (GPU) chips involves advanced packaging technologies that radically alter traditional design methodologies and flows. Designers of high-speed components are called to co-simulate die, interposers, and package to sign off for their products' signal integrity (SI)… Signal Integrity Issues for Silicon Interposers

-

-

Thermal Integrity Challenges and Solutions of Silicon Interposer Design

In this latest installment of the year-long 3D-IC webinar series, Dr. Lang Lin will discuss the Thermal Integrity issues associated with 3D-IC designs. The presentation will cover thermal hotspots, mechanical stresses induced by thermal issues, and methods for capturing these problems with simulation and virtual prototyping, with a focus on designs that utilize silicon interposers.… Thermal Integrity Challenges and Solutions of Silicon Interposer Design

-

Siemens Tessent DFT Forum 2023 India

Hotel Radisson Blu Marathalli ORR, Bengaluru, IndiaAbout Siemens Tessent DFT Forum 2023 India Presenting silicon lifecycle solutions from Siemens EDA: Engineering a smarter future faster Join us for the Siemens Tessent Design-for-Test (DFT) India Tech Forum, being held in Hotel Radisson Blu, Marathalli ORR, Bengalur India, on 29th March, 2023 learn from Industry leaders, fellow designers and experts from Siemens about how to leverage the Tessent… Siemens Tessent DFT Forum 2023 India

-

-

Power Integrity Issues and Solutions for Silicon Interposers

Join us on May 17 for the latest 3D-IC webinar series, “Power Integrity Challenges and Solutions for Interposer Design.” The discussion will focus on interposer power analysis as an isolated case and in context with the dice instantiated in a 3D-IC device. The presentation will then explore the completed multi-chip design in a system simulation.… Power Integrity Issues and Solutions for Silicon Interposers

-

-

3D-IC Foundry Frameworks

Join us on July 20th; Ansys R&D members will discuss an overview of the 3D-IC technology development frameworks offered by TSMC, Samsung, and Intel and how Ansys simulation tools and workflows fit into those frameworks. About this Webinar Semiconductor applications such as Mobile (5G), Automotive, and Datacenter (HPC, AI) demand better scaling, performance, and lower… 3D-IC Foundry Frameworks

-

Solution for 3D-IC Interposer Signal Integrity

Our upcoming CadenceTECHTALK: Solution for 3D-IC Interposer Signal Integrity is designed to teach engineers to translate a GDSII stream format (GDSII) file and partition it into simulation blocks for the Clarity 3D field solver. First, you will learn to use GDS-supporting files to simplify GDS to SPD translation and reuse those files to make the… Solution for 3D-IC Interposer Signal Integrity

-

-

The Era of Software-Defined Everything: Chiplets and Bespoke Silicon

From fintech to automotive, defense to healthcare, everyone wants bespoke computing platforms to build "software-defined solutions" that are differentiated in their respective markets. Sign up and save your spot for this special presentation. Overview With the advent of 3D ICs and heterogeneous semiconductor integration, mapping a system on a customized chip/hardware is accessible to "everyone.”… The Era of Software-Defined Everything: Chiplets and Bespoke Silicon

-

DFT for chiplets & 3D ICs using Tessent Multi-die

3D IC (2.5D/3D) designs are on the rise. Design for Test (DFT) for chiplets must be general purpose so they can be tested stand alone and easy to test after assembly into 2.5D or 3D devices. In this webinar you will learn how to use Tessent Multi-die and still adhere to standards like IEEE 1149.1,… DFT for chiplets & 3D ICs using Tessent Multi-die

-

-

Addressing 3D-IC Power Integrity Design Challenges

Power network design and analysis of 3D-ICs is a major challenge because of the complex nature and large size of the power network. In addition, designers must deal with the complexity of routing power through the interposer, multiple dies, through-silicon vias (TSVs), and through-dielectric vias (TDVs). In this webinar, you will learn how the Cadence… Addressing 3D-IC Power Integrity Design Challenges

-

-

CadenceTECHTALK: Driving Intelligent System Design with 3D-IC Multiphysics

As the industry reaches the limits of device scaling at advanced nodes, there is a growing demand for increased computing performance and data transfer in hyperscale data centers and AI designs. Advanced systems-on-chip (SoCs) are approaching the maximum size limits, and there is a need to find innovative solutions to continue scaling according to Moore's… CadenceTECHTALK: Driving Intelligent System Design with 3D-IC Multiphysics

-

Accelerating SoC Automotive Design with Chiplets

Step into the forefront of innovation with our upcoming webinar, which explores how chiplet technology is revolutionizing the automotive industry and setting new benchmarks. Discover how Cadence is empowering customers to achieve unparalleled success with chiplets. Here's what you can look forward to: Mastering Chiplet Architecture: Dive into the intricacies of mastering chiplet architecture, where… Accelerating SoC Automotive Design with Chiplets

-

Signal and Power Integrity Challenges in Advanced Packaging Technologies for Disaggregated Integration

Abstract The integrated circuit industry faces new challenges as chip complexity and area have been increasing to prohibitive ranges. Some segments have been adopting then a relatively new paradigm for heterogeneous integration based on chiplets at the first package level in combination with advanced 2.5 and 3D packaging technologies. The chiplet approach has the advantage… Signal and Power Integrity Challenges in Advanced Packaging Technologies for Disaggregated Integration