PCIe

Events

-

-

How Synopsys Interface IP and Arm Interoperate to Accelerate System IO and Memory Performance

In this webinar, Synopsys and Arm describe how their recent collaboration helps maximize system performance and shorten Arm-based SoC design cycles. Learn how to minimize HPC/data center SoC design risk and ensure end-to-end IP integration, using available Arm reference designs and interoperability reports. Find out how Synopsys’ interface IP for the most widely used protocols…

-

-

Defending the Cloud: PCIe and CXL Data Security for High-Performance Computing

Cloud computing is going through a significant overhaul and continues to grow globally with increasing presence of hyperscale cloud providers for big data, high-performance computing (HPC), and analytics. In-house data centers are increasingly going off-premise, resulting in the co-location of data centers that manage and store data for companies and application developers to improve scalability…

-

-

CXL and IDE: Important Considerations of Protecting High Speed Interconnects

In a few short years, CXL (Compute Express Link) has evolved from an idea to a rapidly proliferating low latency interconnect standard being adopted into data centers, high performance computing, and cloud computing. However, as the adoption has increased, so has the security threat model users face. To address this, the CXL 2.0 standard has…

-

-

PCIe 6.0 From IP to Interconnect in High-Performance Computing

ABSTRACT: PCI Express (PCIe) is one of the most popular interface technologies in the world. Interconnects for high-performance computing (HPC) in the data center, cloud and AI edge continue to increase in speed and density. System architects, SoC designers, PCB developers and SI engineers are challenged as never before to implement bleeding edge solutions. In…

-

-

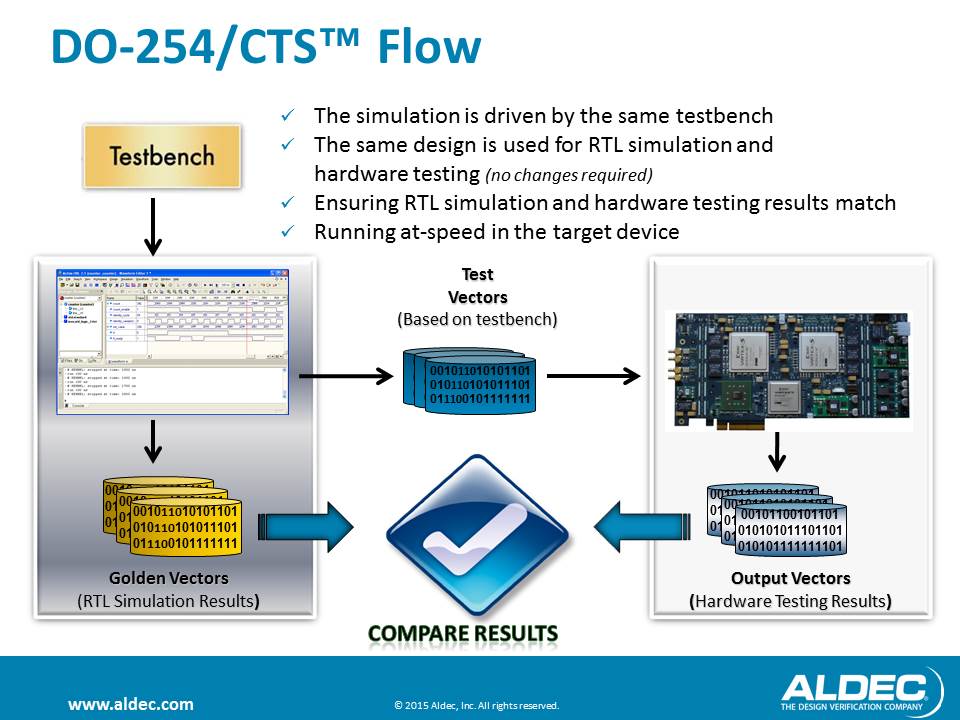

Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance (US)

PCIe-based FPGA designs are becoming popular within avionics systems. However, the verification of such designs for DO-254 compliance with design assurance level (DAL) A or B is problematic. FPGA designs that use asynchronous clocks with multiple high-speed serial interfaces such as PCIe produce non-deterministic results during physical tests. Simulation results are optimized because they are…

-

-

Overcoming PCIe 6.0 System Integration and Pre-Silicon Validation Challenges

PCIe, the most popular interconnect in compute, AI and storage systems, is now offering faster data rate, higher performance, lower power and lower latency than the previous generation. Because of these reasons and the addition of PAM-4 signaling, challenges such as signal integrity, power integrity, implementation, IP integration and more must be considered when designing…

-

-

Evaluating UCIe based multi-die architectures to meet timing and power constraints

Multi-die architectures have evolved from proprietary to industry standard UCIe. UCIe can accommodate the bulk of designs today from 8 Gbps per pin to 32 Gbps per pin for high-bandwidth applications from networking to Hyperscale data centers. To help your UCIe adoption journey, we present VisualSim Architect and the associated UCIe/PCIe6.0 IPs to explore and…

-

-

The Power of SystemVerilog’s DPI

The programming interfaces of logic simulators are largely the domain of specialists writing proprietary tools and extensions and are only vaguely in the consciousness of many design and verification engineers, if aware at all. Yet the simplest use of such interfaces opens up a whole world of possibilities in extending what is achievable in verifying…

-

-

Comprehensive PCIe Verification Solution for bleeding edge and mission critical SoC & IP Designs

Applications such as Data Centers, High-Performance computing (HPC), artificial intelligence/machine learning (AI/ML), cloud computing, military, and aerospace, automotive, etc. are all extremely Bandwidth-hungry. To cater to such high demands of high speeds and bandwidth requires a breakthrough that HPC SoCs are constantly facing. High speed interfaces like PCI Express® (PCIe®) 5.0 and 6.0 show promising…

-

-

Keysight EDA Connect World Tour: Santa Clara – High Speed Digital

Keysight Technologies 5301 Stevens Creek Boulevard, Santa Clara, CA, United StatesShift Left with the Modern Design Center Artificial intelligence (AI) is redefining high-speed digital designs. Your ability to design, simulate, and test — using an automated, integrated workflow — is what will set you apart. Whether you are a design team leader, digital designer, or system engineer, this one-day event is for you. We have…

-

-

ARM corelink, Arteris NoC, UCIe, Bunch-of-wires, CXL and PCIe- Designing the interconnect is not for the weak-hearted

There are so many options for Network-on-Chip: ARM-Corelink CMN700, Arteris FlexNoC, open-source NoC interconnect, and of course developing home-grown fully customized solutions. Where does each solution fit? Where do we use it- backplane vs inside domains? How does AMBA AXI or PCIe or CXL fit in the mix? With the advent of chiplet, do we…